# Australian Black Box Electrical System for Recording and Later Recovery of Cockpit Voice and Flight Data in March 1962 Validation Flight Test

by

# K.F. Fraser Retired Principal Research Scientist Defence Science and Technology Group Melbourne

Date of original document: 28 October 2023

Date of this revision: 5 September 2025

# **Summary**

This document relates mainly to the electrical aspects of the Australian Flight Memory System (FMS) for which Dr David Warren is the recognized inventor. That system was designed to demonstrate a capability that would greatly assist airplane accident investigators in their determination of the cause of such accidents. The FMS was the first in the world to include both Cockpit Voice and Flight Data recording. An equivalent present-day device is normally referred to as a Black Box. Such Black Boxes are almost universally regarded as electrical items although there are some non-electrical survivability aspects.

Two versions of the FMS were flight-tested, one in 1958 and the other in 1962. The purpose of this document is to provide circuit descriptions and associated analyses of the complete 1962 FMS within a single file. The FMS comprised three main items: magnetic wire recorder, airborne signal processor and ground station processor. Deficiencies in available electrical circuits for the first two items complicated the production of this document, particularly as the author is the only living person who had made a major contribution to the FMS. These deficiencies were accounted for by the author's substitution of on-paper design of circuits that could have met the requirements in 1962. Mathematical analyses of various items are included where appropriate to either enable unknown circuit values to be calculated or to assist in the understanding of the operation of some elements.

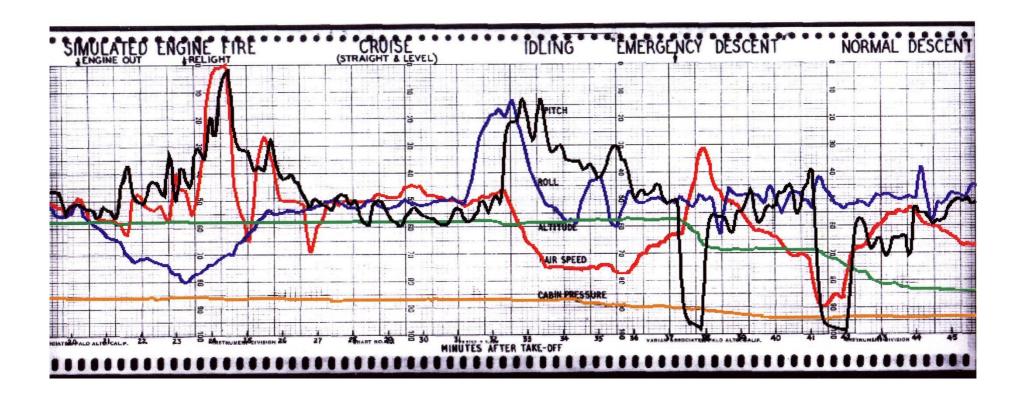

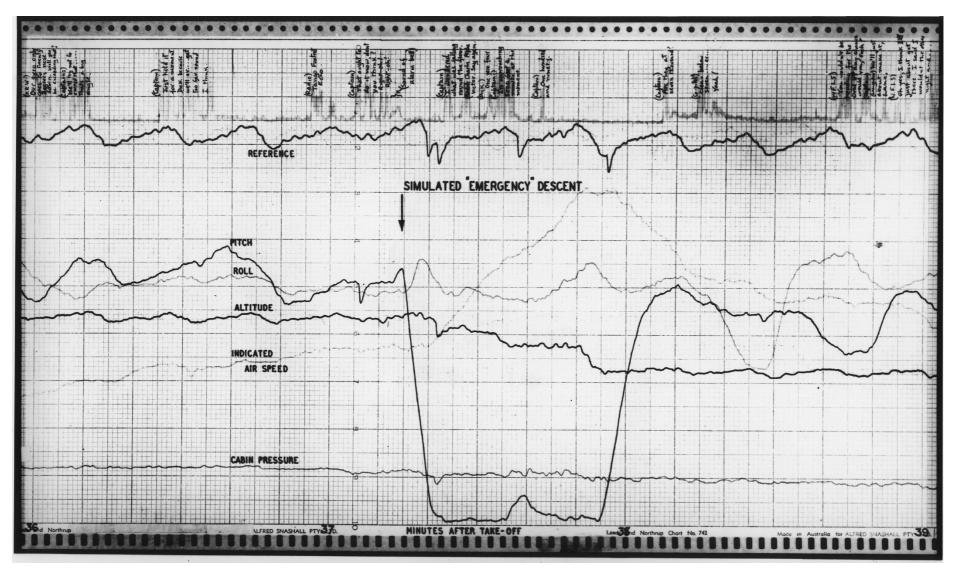

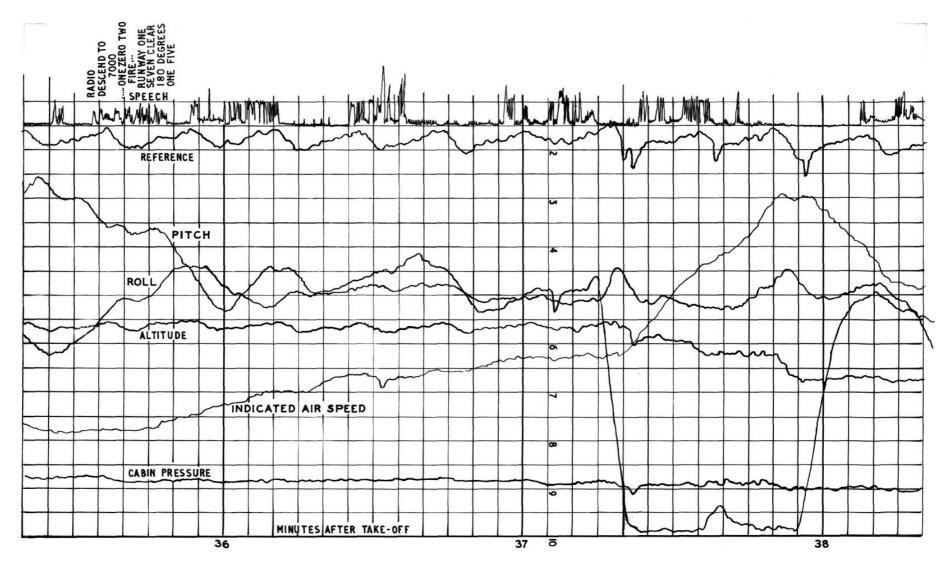

Analogue and digital presentation of the results from the 23 March 1962 successful flight validation test of the FMS are included in this document.

#### **Contents**

#### About the Author

#### **Main Text**

#### Part A: Start Items

- 1. Introduction

- 2. Invention History

- 3. Overview of Flight Memory System and Participants

# Part B: Airborne System Signal Recording

- 4. Airborne System.

- 4.1 Recorder

- 4.1.1 General

- 4.1.2 Magnetic Wire Movement

- 4.1.3 Electrical Elements

- 4.2 Cockpit Voice and Flight Data Handler

- 4.2.1 External Inputs for Electronics Unit

- 4.2.2 Electronics Unit

- 4.2.2.1 Signal Processor

- 4.2.2.1.1 Cockpit Voice Signal Processor

- 4.2.2.1.1 Pre-Amplifier

- 4.2.2.1.2 Band-Pass Filter

- 4.2.2.1.3 Clipper

- 4.2.2.1.2 Flight Data Signal Processor

- 4.2.2.1.2.1 Clock Pulse Generator

- 4.2.2.1.2.2 Multiplexer

- 4.2.2.1.2.3 Analog Output Offset Producer

- 4.2.2.1.2.4 Pulse Duration Modulator (PDM)

- 4.2.2.1.2.5 Sine-Wave Amplitude Modulator

- 4.2.2.1.3 Cockpit Voice and Flight Data Output Generator

- 4.2.2.1.3.1 Combiner

- 4.2.2.1.3.2 Combined Signal Recording

- 4.3 Airborne Power System

- 4.3.1 Overview

- 4.3.2 Power Source Controller

- 4.3.3 Provision of DC Output

- 4.3.3.1 Requirement

- 4.3.3.2 Inverter

- 4.3.3.3 Regulated DC Power

- 4.3.3.4 Unregulated DC Power

- 4.3.4 Provision of AC Output

#### Part C: Ground System Signal Recovery

- 5. Ground System

- 5.1 Playback Signal Source

- 5.2 Flight Memory Ground Station Unit

- 5.2.1 Pre-Amplifier

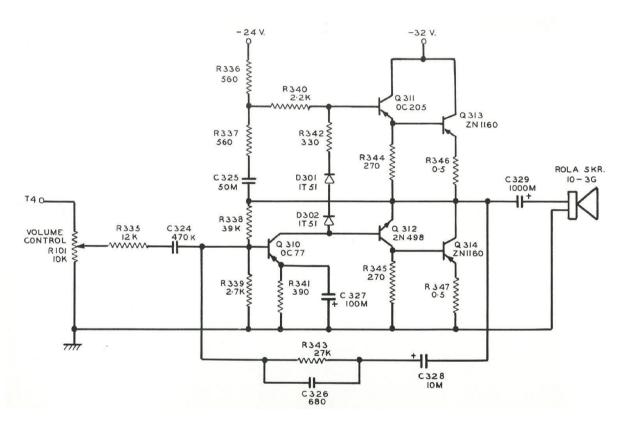

- 5.2.2 Cockpit Voice Processor

- 5.2.2.1 Cockpit Voice Extractor

- 5.2.2.2 Cockpit Voice Power Amplifier and Speaker

- 5.2.2.3 Cockpit Voice Voltage Level Indicator

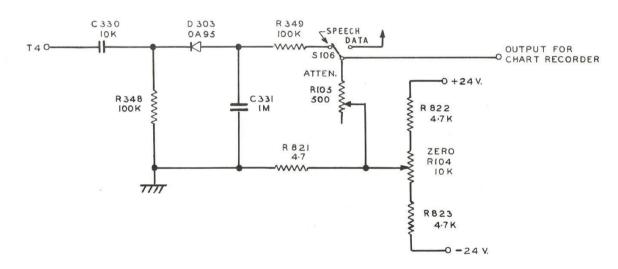

- 5.2.3 Flight Data Processor

- 5.2.3.1 Flight Data Extractor

- 5.2.3.2 Flight Data System After Extractor

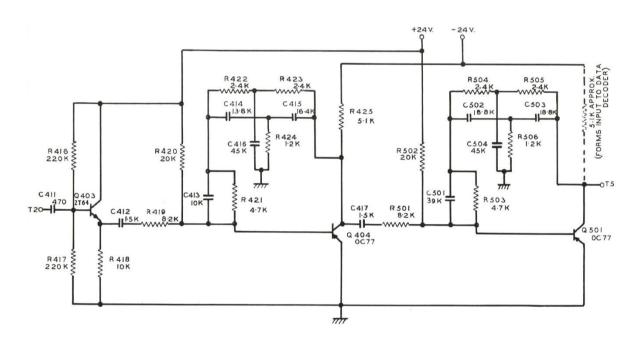

- 5.2.3.2.1 Flight Data Decoder

- 5.2.3.2.1.1 Frequency Doubler

- 5.2.3.2.1.2 Pulse Duration Replicator

- 5.2.3.2.1.3 Ramp Generator

- 5.2.3.2.1.4 Synchronised Oscillator

- 5.2.3.2.2 Flight Data Output Generator

- 5.2.3.2.2.1 Voltage Comparator

- 5.2.3.2.2.2 Binary Counter

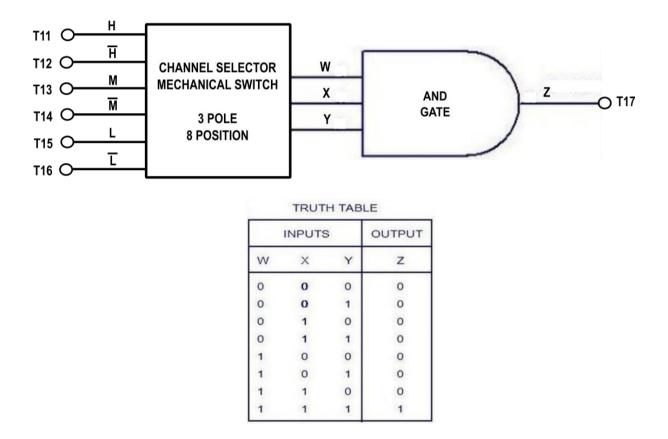

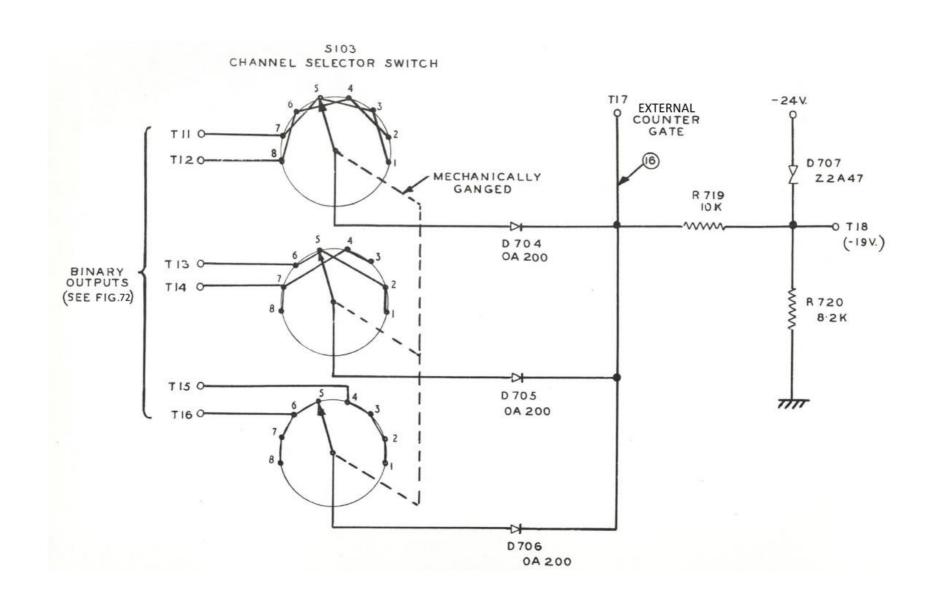

- 5.2.3.2.2.3 Channel Selector and Digital Presentation of Data

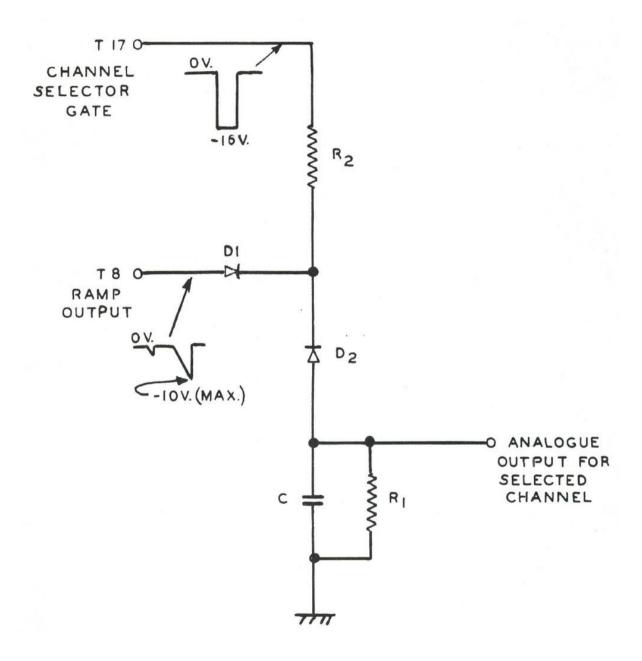

- 5.2.3.2.2.4 Analogue Output Generator and External Presentation of Data

- 5.2.3.2.2.5 Possible Simple Extension of the Ground Station Unit (GSU)

- 5.2.4 Power System for Ground Station Unit (GSU)

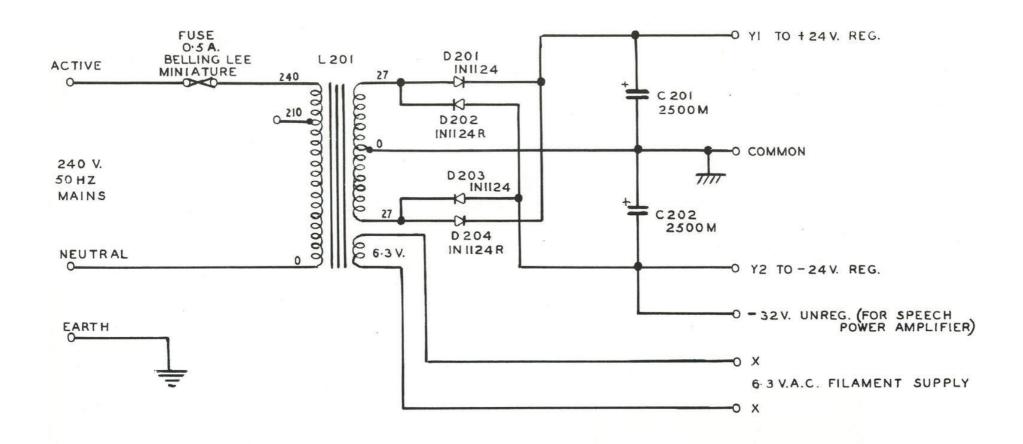

- 5.2.4.1 Power Transformer and Rectifier-Filter Unit

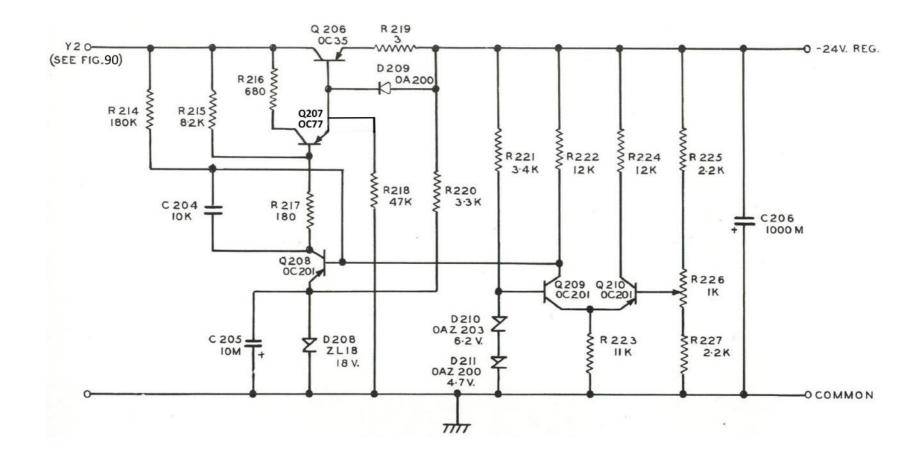

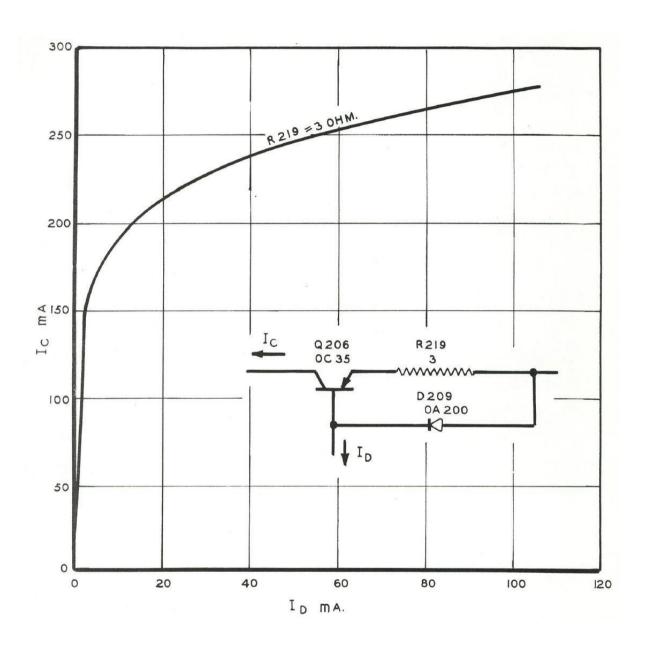

- 5.2.4.2 –24 Volt Regulator

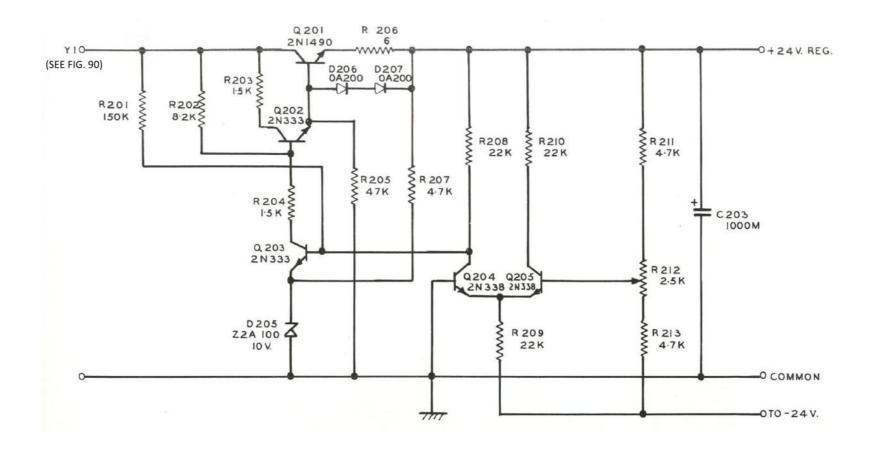

- 5.2.4.3 +24 Volt Regulator

- 5.3 Review of Flight Memory System Data Recovered from the 23-March-1962 Flight Test

- 6. Other Contributions

- 6.1 Author's Website

- 6.2 Flight Memory Summary Document

- 6.3 Other Documents

- 6.4 Book by Janice Witham

- 6.5 Photographs

- 6.6 Lawrence Hargrave Award

- 6.7 Films & Audio

- 6.8 Stage Play

- 7. Influence of Australian Flight Memory System on Local and Overseas Markets

- 7.1 Recognition of Dr Warren as Black Box Inventor

- 7.2 Flight Memory Related Black Box Developments Locally and Overseas

- 7.3 Comparison of Australian Flight Memory System with Later Black Box Versions

# 8. Concluding Remarks

# Acknowledgements

# References

# **Appendices**

| Appendix 1: A | Amplifier | Basics |

|---------------|-----------|--------|

|---------------|-----------|--------|

- Appendix 2: Cockpit Voice Processor Stop Band Attenuation Slopes

- Appendix 3: Alternative Airborne Electronics System Clock Pulse Generator

- Appendix 4: Analog Output Offset Producer Calculations

- Appendix 5: Pulse Duration Modulator Trigger Delay Analysis

- Appendix 6: Analysis of Effect of Using Pulsed Sine-wave Flight Data Modulation

- Appendix 7: Decision that Had Major Impact on Power System Development

- Appendix 8: Analysis of the Ground Station Flight Data Extraction Process

- Appendix 9: Simultaneous Multiple-Channel-Analogue Output Selection Circuit

Figures 1 to 100 for Main Text

Figures A1 to A12 for Appendices

#### **About the Author**

The author, Mr Kenneth Francis Fraser, graduated from the University of Melbourne (Australia) in 1958 with Second Class Honours in a four-year Bachelor of Electrical Engineering (BEE) degree. There were 33 students in the final year and there was one First Class recipient, three Second Class recipients, and the author does not recall how many Third Class recipients there were. The author was ranked third in the Honours list. In third year the author received the Exhibition (ranked first) in Engineering Design for which there was a small monetary award.

At the end of the third year of the BEE degree course, the author was employed for some months as a vacation student at the Aeronautical Research Laboratories (ARL) at Fishermans Bend (a suburb of Melbourne). At the time, ARL was part of the Commonwealth Department of Supply (in 1974 ARL was shifted to Department of Defence). Later changes have resulted in the ARL name no longer being in use. The author was impressed with the type of work and the working conditions, and sought (by phone contact with the supervising scientist for whom he reported to during vacation employment) to gain employment after graduation in 1958.

Early in 1959 the author was in contact with the supervising scientist who indicated, to the author's surprise, that he had managed to recruit two assistants for him and he could now report for duty. So it was that he commenced duties (without a formal scientific suitability interview) in February 1959. At that time the graduate scientific staff were in Experimental or Scientific Officer grades. To gain entry to the Scientific Officer grade required either a PhD or a Bachelor's Degree with at least a Second Class Honour. The author thus met the minimum requirement for Scientific Officer grade. Later the Scientific Officer term was changed to Research Scientist. The author progressed through the ranks to Principal Research Scientist and retired in 2002 at age 65. Soon after the author's retirement, the Research Scientist and Experimental Officer grades were abolished and scientific staff progressed through a single stream based on performance.

After retiring the author extended his interest in computer programming, as a leisure activity, by becoming more proficient in C++ and Java computing languages. He applied these in the generation of software to solve Rubik's style cubes of large size. In 2010 he made those programs publicly available by the creation of a website <a href="www.kenblackbox.com">www.kenblackbox.com</a>. Some further developments since 2010 were believed by the author to be the most advanced in the world when they were made publicly available. Of particular significance was the software extensions for implementing and solving cubes with marked centres (super-cubes) over a wide cube-size range.

His website included some background on selected scientific achievements during his employment throughout the 1959-2002 period. Of particular significance was his work relating to the ARL Flight Memory (Black Box) which was the invention of Dr David Warren with whom the author had a close working relationship. The author has attempted to keep an up-to-date listing of Flight Memory items (documents, films, events, photographs etc.) in the one place (refer to <a href="www.kenblackbox.com/blackbox.htm">www.kenblackbox.com/blackbox.htm</a>) and there would appear to be an endless procession of such items.

The motivation to report on the electrical aspects of the Flight Memory system was a request to do that by a close friend who has agreed to maintain the above-mentioned website when the author is no longer able to do that.

# **Main Text**

# **Part A: Start Items**

#### 1. Introduction

Dr David Ronald de Mey Warren (20 March 1925 – 19 July 2010) was an Australian scientist, widely recognised as the inventor of the aircraft Black Box accident recorder which comprises a Cockpit Voice Recorder (CVR) and a Flight Data Recorder (FDR). He called his invention "Flight Memory". The term *black box* generally refers to a complex system or device whose internal workings are hidden or not readily understood. The Black Box label for aircraft accident recorders was introduced by a journalist and has since been widely adopted for general public recognition, not only for aircraft but other transport systems as well.

Dr Warren was a combustion and fuels specialist. He was employed as a research scientist at the Aeronautical Research Laboratories (ARL) in Melbourne. At that time ARL was a branch of the Commonwealth Department of Supply. In 1974 ARL became part of the Department of Defence. In the mid-1950's Dr Warren was involved in the accident investigations related to the mysterious crash of the world's first jet-powered commercial aircraft, the Comet. It occurred to Dr Warren that it would be extremely useful if there had been a recording of what had happened in the aeroplane immediately prior to the crash. Dr Warren then recalled the world's first miniature recorder that he had recently seen at a trade fair. He could visualise such a recorder placed in all aircraft, continually recording details and able to be recovered after a crash.

The reason why Dr Warren's expertise was sought for the Comet crash investigations was because of his combustion knowledge – could there have been an in-flight fire? Most people would consider the aircraft Black Box to be an electrical device. That in the main is true but there are other important structural elements such as design to withstand fire, impact and water immersion. The fire proofing was one that Dr Warren was endowed with the specialist skill to achieve.

While Dr Warren was a very smart user of electrical or electronic devices, he needed electrical specialists to develop airborne recording and ground station recovery systems to validate the invention and show the results. The main aim of this document is to describe the electrical systems used in the 23 March 1962 system flight test. Many aspects of the design have never previously been documented and the author does not have complete details.

All Flight Memory system items with electrical input or output will be examined in this document. Most are electronic (using semiconductor diodes and transistors) but non-electronic electrically-related items including a motor, a battery-pack, transformers, relays, microphones, a lamp, transducers etc. will also be examined

#### 2. Invention History

Dr Warren's earliest involvement in aircraft accident recording was in 1953 and his idea was documented (Ref. 1) in April 1954. In 1998 Dr Warren and the author produced a document (Ref. 2) that provided a brief summary of the invention and its in-flight validation.

In 1958 Dr Warren reported (Ref. 3) on extensive cockpit microphone tests he had undertaken (probably in 1957) on Vickers Viscount and Douglas DC-6B planes under arrangements provided by the Department of Civil Aviation. He concluded that good intelligibility could be achieved with optimum microphone choice and placement, and using noise cancelling arrangements.

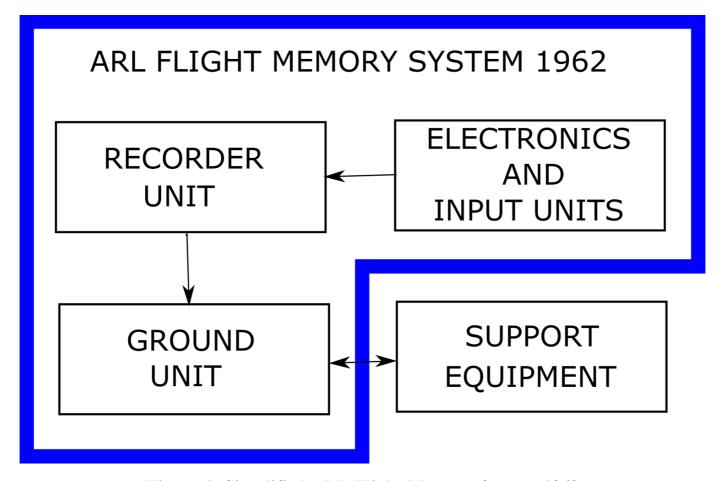

In 1958 a magnetic wire recorder was built by instrument maker Mr Tych Mirfield under a Commonwealth Government contract arranged by Dr Warren. The magnetisable steel wire had 0.05 mm diameter and was the same as that used in the German Minifon miniature audio recorder. The ARL recorder was fully automatic for fit-and-forget operation with a "memory" mechanism that would store four hours of pilot voice and eight instrument readings at the rate of four per second up to the moment of any accident, but would automatically erase older recording for the wire to be re-used. Wire rather than tape was chosen by Dr Warren because of its compact size and its ability to withstand much higher temperatures than tape. Dr Warren claimed that this system (let us call it Mk 1) was successfully flight tested in 1958. However, the overall design was fairly rudimentary and in some respects its performance was deficient. There appears to be a lack of documentation on the electrical circuits used and the results of the flight test.

With the Mk 1 recorder on-hand in 1958, the lack-of-interest stalemate was finally broken in that year when the Secretary of the UK Air Registration Board, Sir Robert Hardingham, happened to see the recorder while on an informal visit to ARL. His enthusiasm was instantaneous. He arranged for Dr Warren to take the recorder to England to demonstrate it. The response to the demonstration in the UK was most encouraging. The BBC featured the recorder on evening television and Radio Newsreel. Many UK manufacturers and operators offered their support, and the British authorities began a move to make recorders mandatory in British civil aircraft.

Progress in Australia had to wait until the unexplained crash of a Fokker Friendship in Mackay, Queensland, in June 1960. The judge inquiring into the mysterious crash was told of the development of the ARL crash recorder and, as a result, made a judicial order that all Australian airliners must carry recorders for pilot speech as from January 1963.

In view of renewed interest in crash recording Dr Warren who worked in the Mechanical Engineering Division of ARL sought the help of electrical/electronic specialists from the Aerodynamics Division to design and build an updated pre-production version of the recording and recovery system with improved performance (let us call the updated version Mk 2).

The involvement of the author (together with two other electrical development staff) for the Mk 2 system development began in early 1961. Details of that development form the major element of this document.

# 3. Overview of Flight Memory System and Participants

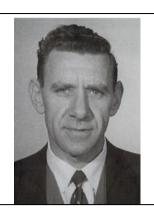

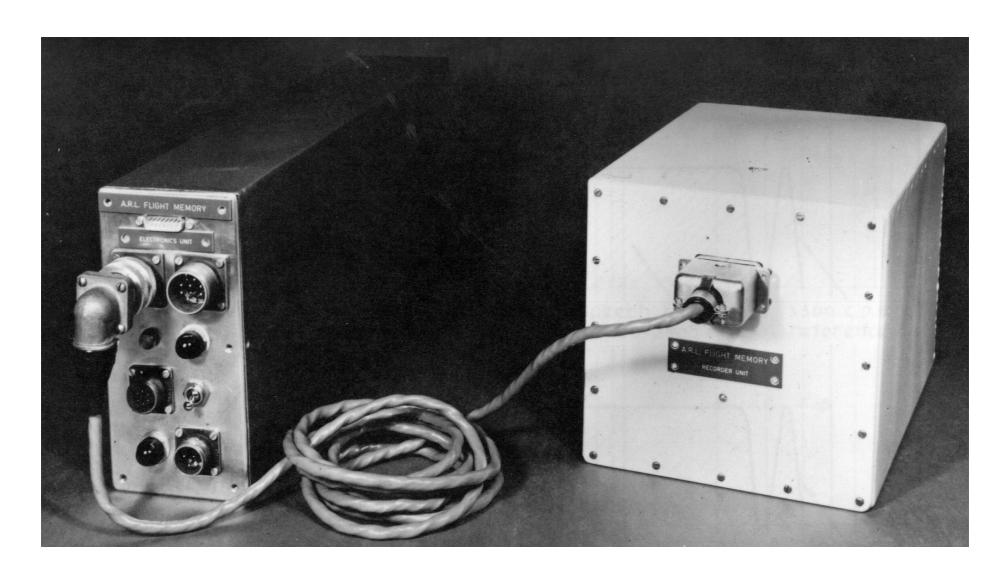

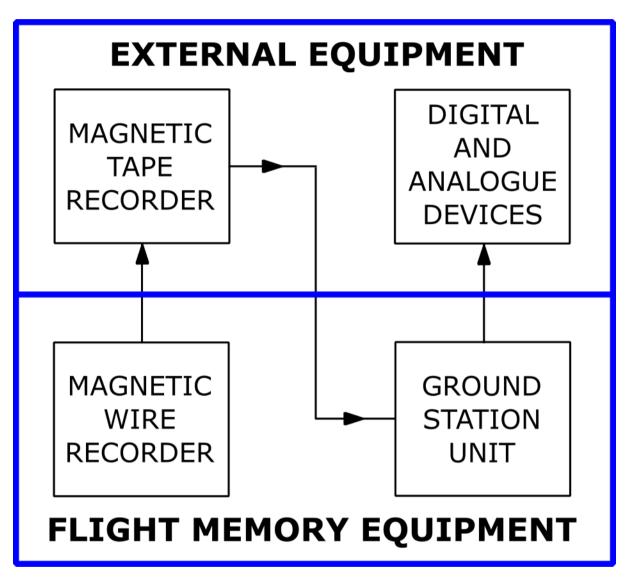

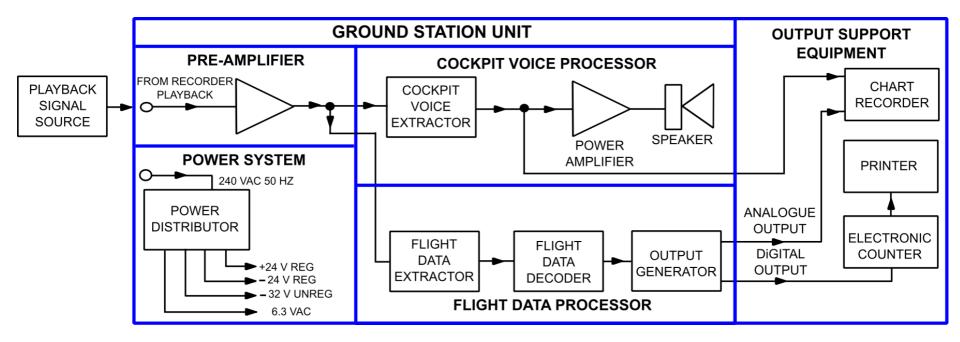

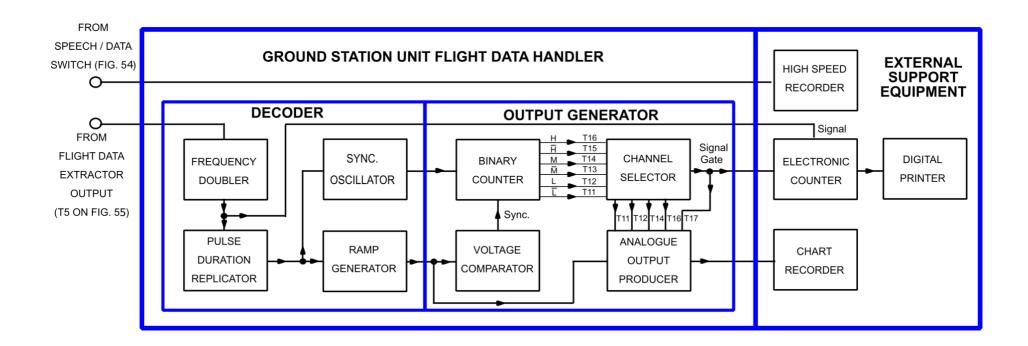

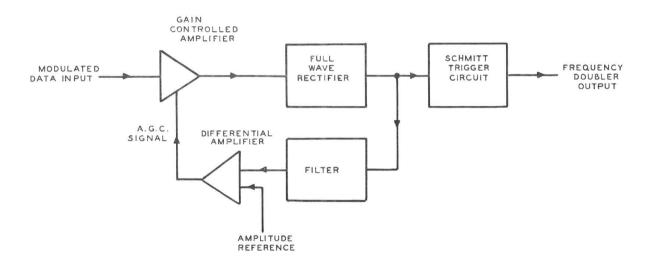

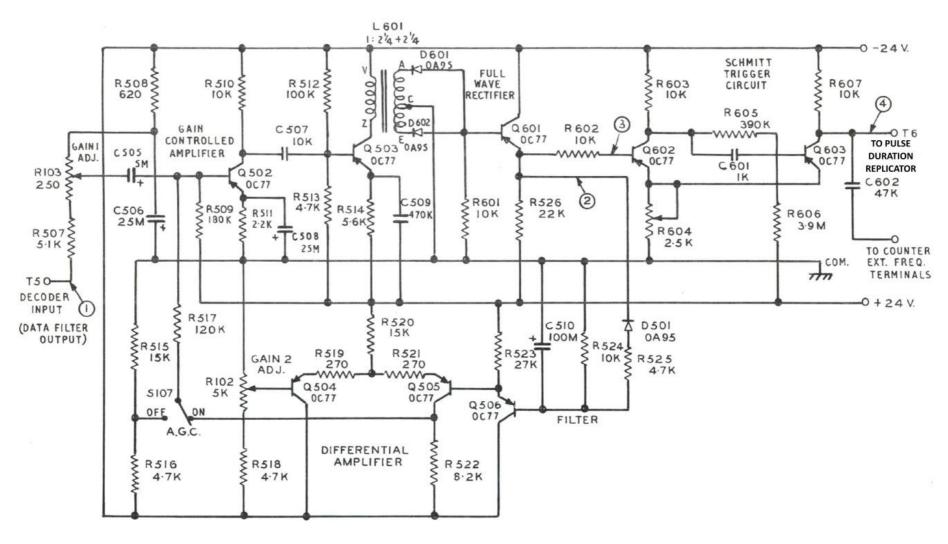

The block schema of Fig. 1 shows the ARL Flight Memory System 1962 comprises three major electrical sub-systems. These are the Recorder Unit and the Electronics Unit which form the on-aircraft data recording system and the on-ground Ground Unit for data recovery. The Support Equipment is considered external to the Flight Memory system. It provides recorded signal input and processed signal output for the Ground Unit. The major contributors and their

involvement in the 1962 system are explained below. The photographs are those taken as close as practical to 1962.

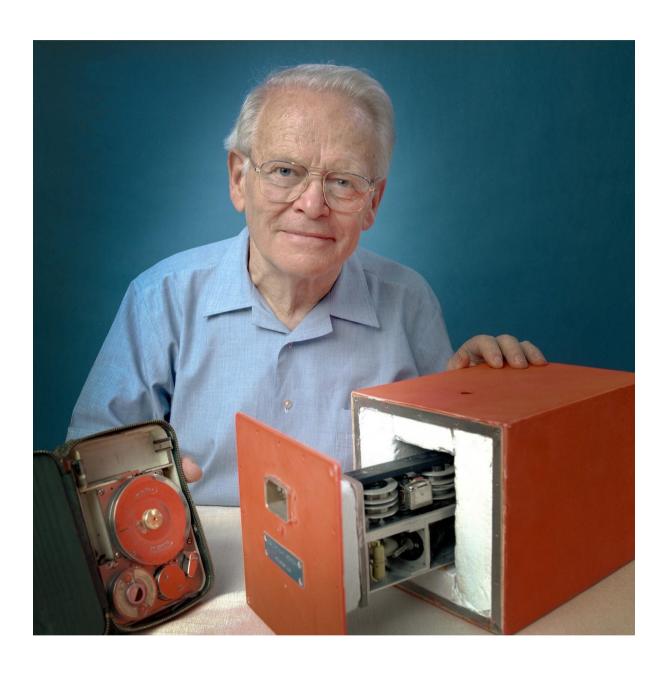

Dr David Ronald De Mey Warren: 1925 – 2010

Dr Warren is widely recognised internationally as inventor of the black box which has a close resemblance to today's boxes. He first published his idea in April 1954. He was a combustion and fuels scientist and a very smart user of electrical devices. He organised the development and production of the recording deck for the 1962 airborne system. He designed the fireproof, impact-proof and waterproof housing for the in-flight recorder. In the workplace he was called Dave.

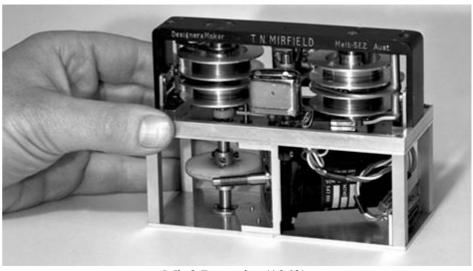

Mr Tych Mirfield (Theon Numa Mirfield at birth): : 1902 – 1972

Mr Mirfield was a smart private-enterprise instrument maker who, under an ARL contract raised by Dr Warren, built the magnetic wire recording deck to meet a requirement specified by Dr Warren. Photo was taken in 1965.

Mr Walter Francis Lane Sear: 1916 – 1983

Mr Sear was an experienced and talented electrical systems developer. In 1961-62 his contributions were the design of the signal processor which represented two thirds of the airborne *Electronics Unit*, and the audio filter which was copied for the *Ground Unit* and represented a significant contribution to that design. In the workplace he was called Lane.

Mr Kenneth Francis Fraser: 1937 –

Mr Fraser was the youngest of the 1961-62 development team His contribution to the airborne *Electronics Unit* was the design of the power system with the main item being provision of power for the *Recorder Unit*. He designed the flight data recovery system for the *Ground Unit*. His overall contribution was one third of the airborne *Electronics Unit* and most of the *Ground Unit*. In the workplace he was called Ken.

Mr Walter Ernest Boswell: 1923 – 1989

Mr Boswell was an experienced and talented technician. In 1961-62 he created the circuit boards containing the individual electronic components for both the airborne *Electronics Unit* and the *Ground Station Unit*. That was at a time before printed circuits were in common use. He used a standard case for the airborne *Electronics Unit* and designed the case for the *Ground Unit*. He also performed the inter-wiring between the boards and the cases in which they resided. In the workplace he was called Wally.

All personnel mentioned above except Mr Mirfield were employed at the Aeronautical Research Laboratories as it was known in 1962. While the Flight Memory project had its share of detractors in 1962, it was strongly supported by Sir Lawrence Coombes (the head of the Laboratories) and Mr Tom Keeble (the head of the Mechanical Engineering Division).

# Part B: Airborne System Signal Recording

# 4. Airborne System

The Airborne System comprises two major hardware units: the magnetic wire Recorder and the Electronics Unit. The latter processes Cockpit Voice and Flight Data. To improve the chance of recovery of the important recorded data after an aircraft accident, it was proposed that the place where the Recorder was located should be carefully chosen (the tail being the most likely location). Recovery of the Electronics Unit after an accident would not be required and so there would not be any restriction on where it could be placed.

#### 4.1 Recorder

The Recorder comprised mechanical, electro-mechanical and electrical components. The author could not find any electrical circuit details for the recorder except for the motor power circuit which will be examined in Sec. 4.3.

#### 4.1.1 General

The recorder used magnetisable steel wire of 0.05 mm diameter (about the size of a human hair) as the recording medium. Magnetic wire recording was in use before magnetic tape recording which became commercially available in the 1950s. The use of magnetic wire was supported by the availability of the German Minifon P55 Type S miniature wire recorder (Fig. 2) which used a nominal wire speed of 13.4 inch per second. An advantage of wire in this application was that it could withstand a higher temperature over a given period of time than magnetic tape and storage capacity per unit volume of storage medium was very good. Disadvantages of wire include that it is single track, there is no capstan to keep wire speed constant as the wire is pulled past the head by the driving spool, and the only way to repair a broken wire is to tie the broken ends in a knot. Another reason for using wire recording was that a miniature tape recorder with the required recording duration was not available when the first ARL recorder was built prior to the 1958 flight test.

Two versions of the ARL Flight M Memory Recorder were produced. The author will refer to these as Mk 1 and MK 2 recorders. The Mk 1 was used in a flight test in 1958 (Ref. 3) and the MK 2 was used in the 1962 flight test (Ref. 2). Photographs of these recorders are shown in Fig. 3. These photographs were taken from opposite sides for the two versions of the recorder. The author does not have photographs of both sides of these recorders for either version.

Insufficient details on the Mk 1 recorder are available to the author. According to the design requirement for the recorder (Ref. 3 p13), the recorder was to be powered by "A 24V dry cell of sufficient capacity to run the recorder for 5-30 minutes". If that proposal were applied, a brush-requiring DC motor would have been used.

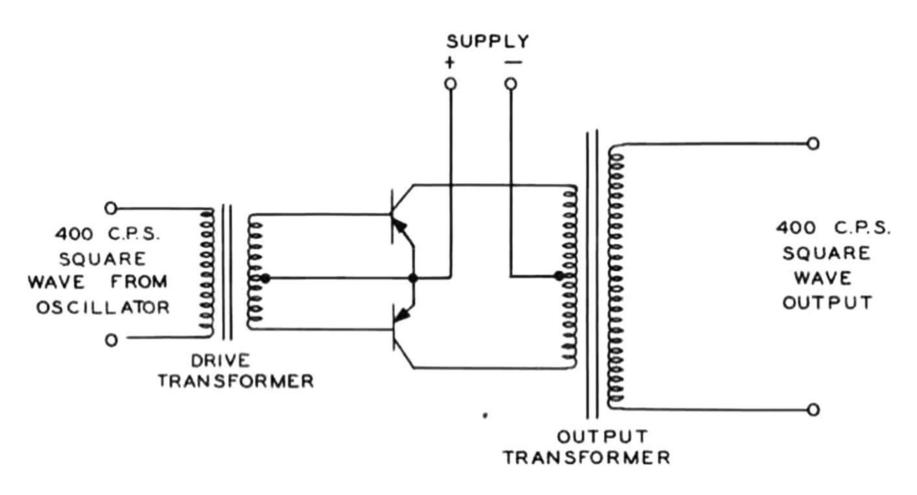

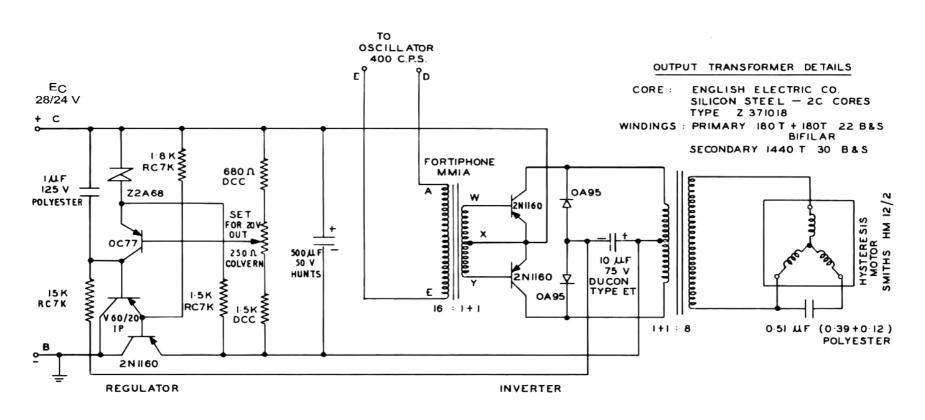

The construction of the Mk 2 Recorder was more robust than that of the Mk 1. A photograph of the Mk 2 Recorder partially inserted into its fire-proof and impact-proof case is shown in Fig. 4. It uses a brush-less four-pole hysteresis motor designed to run from three-phase 400 Hz power, which is available as standard from aircraft inverters. Hysteresis motors run at synchronous speed which equals supply power frequency divided by half the number of poles. It was known that the required speed of the motor was 1200 RPM. Hence the motor would have to run at 200 Hz if powered from standard aircraft AC power. Except for the different

motors, the author believes the remainder of the recording unit for the Mk 1 and Mk 2 versions to be similar. The airborne systems comprise mechanical, electro-mechanical and electrical elements.

#### 4.1.2 Magnetic Wire Movement

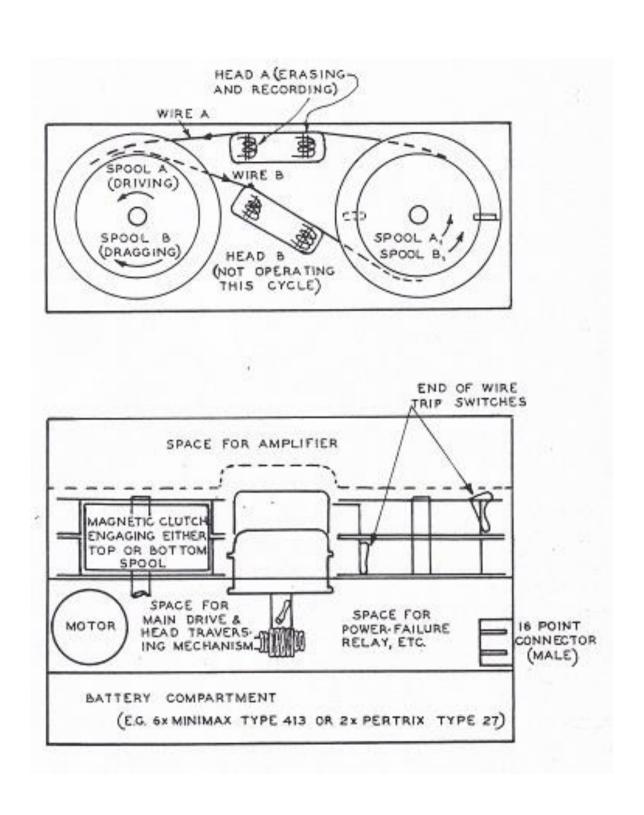

The basic requirement of the recorder as envisaged by Dr Warren on 8-Aug-1958 was that it would record in a continuous loop erasing just before recording. An innovative mechanism (Fig. 5) was required to meet this requirement. The author believes that mechanism with some minor modifications would have been used in both Mk 1 and Mk 2 Recorders. Electrical components are clearly visible (Fig. 5) on the lower panel for the Mk 1 Recorder. Whether batteries are also present is unclear. There is no lower panel for the Mk 2 Recorder. The recording duration for the Mk 2 Recorder was four hours.

The design of the ingenious mechanical mechanism relating to the movement of the magnetic recording wire is a significant achievement for Dr Warren and Mr Mirfield. The magnetic wire movement will be described here in three parts: Spool Rotation, Wire Stacking and End-Of-Wire Detection.

## Spool Rotation

The rotational arrangement is illustrated in the top figure of Fig. 5 (which is a copy of Figure 13 in Ref. 3). The top pair of spools are designated as Set A and the bottom pair as Set B. At any time one spool is locked onto its motor-driven central shaft and drives all spools. Rotation markings in Fig. 5 are for the left Set A spool as the driver spool for which its wire is in recording mode. All spools except the driver spool move freely about their central shaft. When the Set B spools are in recording mode all the arrows in Fig. 5 are reversed with the Set B left spool now locked onto its central shaft for which its direction of rotation remains unchanged.

#### Wire Stacking

The stacking of the wire onto the driving spool and unstacking it from the take-up spool is a complication not applicable to magnetic tape recording. The stacking arrangement is depicted in the bottom figure of Fig. 5. The panel on which the head sets are mounted moves up and down relative to the spool sets so that the wire is always correctly aligned with the heads. Think of each layer as being similar to a tightly compressed linear spring with helical coil.

#### End-Of-Wire Detection

The End-Of-Wire trip switches are depicted in the bottom figure of Fig. 5. The switches are located in the right-hand spools. It is assumed that the trip-switches are mechanically-operated electrical-input on/off switches. The switches appear to be closed when wire in on the spools but are momentarily opened at the end of the reel when not held closed with wire. The author has no details on these switches. Switch possibilities include an identical switch to that used in the Minifon wire recorder and a specially made switch by Mr Mirfield. The switches may have been spring-loaded.

#### 4.1.3 Electrical Elements

The AC motor has been mentioned above and will be examined further in Sec. 4.3 relating to the Airborne Power System. Electrical circuits relating to erase-head erasing and record-head signal recording will be included in Sec. 4.2.2.1.3.2 Combined Signal Recording. The main item to be considered here is the provision of the clutch control signals.

The author has no electrical circuit diagram for either the Mk 1 or the Mk 2 Recorder. In a Minute written on 8 August 1958 "assistance with the [Mk 1] electrical system design by Mr W.G. Cadzow" (deceased), an ARL employee, was recognised. Mr Cadzow proposed to write a Technical Memorandum on his contribution titled "Transistorised flight data and speech equipment for a crash recorder". It has been confirmed that the proposed document was never published.

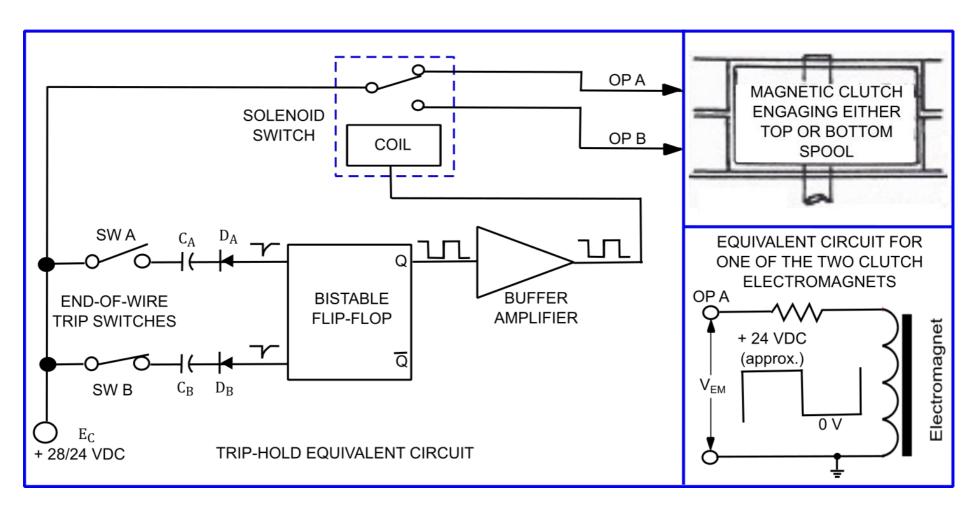

According to the Design Considerations (Ref. 3 p 11) for the Mk 1 Recorder, the use of "a two-sided magnetic clutch between the spools" is recommended and "it can be operated by a simple end-of-wire trip switch". It is assumed that the trip-switches are mechanically-operated electrical-input on/off switches. It is known (Fig. 5) that the clutches are magnetic. Whether to use permanent magnets or electro magnets would have been the first consideration. The author believes the electro-magnet option would have been chosen as that approach would render the clutches more readily controllable. Control would be by electrical input. Because the trip-switches would be off only momentarily a means would need to have been provided to hold each clutch active for a full cycle (2 hours) and then inactive for the next 2-hour-cycle.

The circuit of Fig. 6 is a hypothetical one drawn by the author to do what he believes was needed to meet the recorder's electrical requirements.

Circuit power is derived from the  $E_C$  input. Normally  $E_C$  is equal to the aircraft DC supply voltage (nominally 28 V) but under the very rare possibility of aircraft DC power failure the Flight Memory emergency battery (24 V nominal) would apply. The Power Switch Controller (Sec. 4.3.2) provides details on the Flight Memory System power switching.

The bistable flip-flop which can be triggered on and off is an obvious choice for use in this application.

A miniature solenoid-operated one-pole changeover switch is shown. Its contacts would have been required to have the capacity to pass the current required for the clutches. The magnitude of that current is not known by the author.

#### 4.2 Cockpit Voice and Flight Data Handler

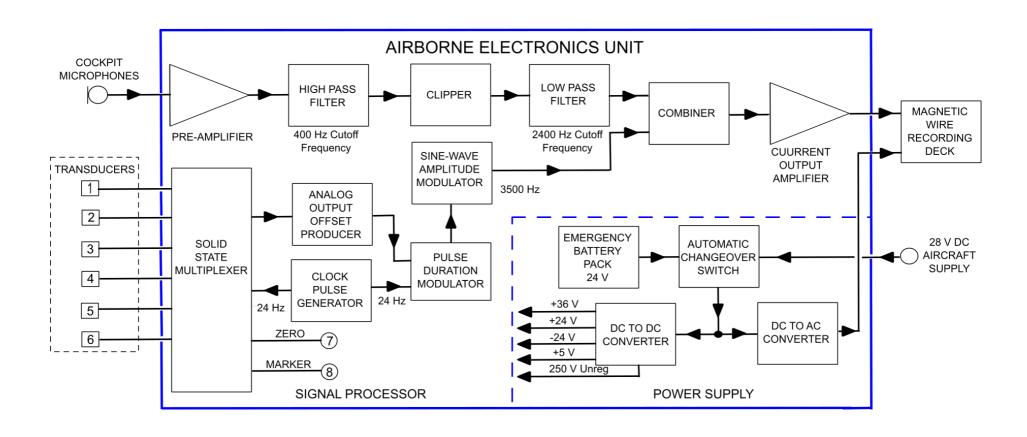

This handler comprises all the Flight Memory electrical system with the exception of the Recorder Unit which was described in Sec. 4.1. With the exception of the Power System there was no other portion of the handler that has been documented previously. A block schema of the Airborne Flight Memory System is shown in Fig. 7. Mr Sear developed the Signal Processor and the author developed the Power System.

#### 4.2.1 External Inputs for Electronics Unit

The External Inputs comprise the Cockpit Microphone, six Transducers and the aircraft 28 V DC supply.

#### Cockpit Microphone

The author does not know what microphone (or microphones) were used for the 23-March-1962 flight test. The selection of microphone and placement was done by Dr Warren. He had performed extensive microphone tests (Ref. 3) in1958. In those tests he concluded that a highly directional microphone to

reduce the impact of extraneous noise sources was required. He concluded velocity type microphones provided better directional performance than pressure types because of their dependence on velocity rather than the pressure of air molecules. The author concluded that a velocity type microphone was probably used.

#### Transducers

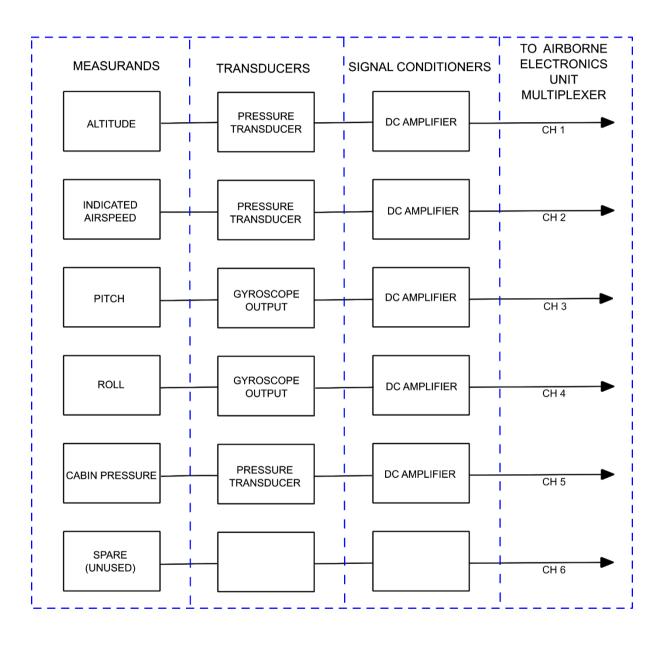

For the 1962 test flight six channels were allocated for aircraft parameter recording but only five were used as indicated in the following table.

| <b>Channel Number</b> | Parameter                |

|-----------------------|--------------------------|

| 3                     | Altitude (ALT)           |

| 4                     | Indicated airspeed (IAS) |

| 5                     | Pitch                    |

| 6                     | Roll                     |

| 7                     | Cabin pressure           |

| 8                     | Spare (unused)           |

|                       |                          |

Ch 1 and Ch 2 were set at fixed voltages within the Airborne Electronics Unit.

A diagram of the transducer system is provided in Fig. 8. The author does not have Make/Model details of the transducers or their associated signal conditioners, including whether they represented a special installations for the test flight (or tapped onto standard aircraft installations). All transducer output signals were constrained to the 0 to 5 V range. The signal conditioners had to accommodate static or slowly changing parameters. Transducer arrangements for the test flight were the responsibility of Mr Don Edwards (deceased) who was a very capable and experienced technical specialist in the transducer field. He was present on the test flight.

# Aircraft DC Supply

Under normal operating conditions power for the complete Flight Memory system would have been derived from the standard 28 VDC aircraft supply. Details on its use is provided in Sec. 4.3 Power System.

# 4.2.2 Electronics Unit

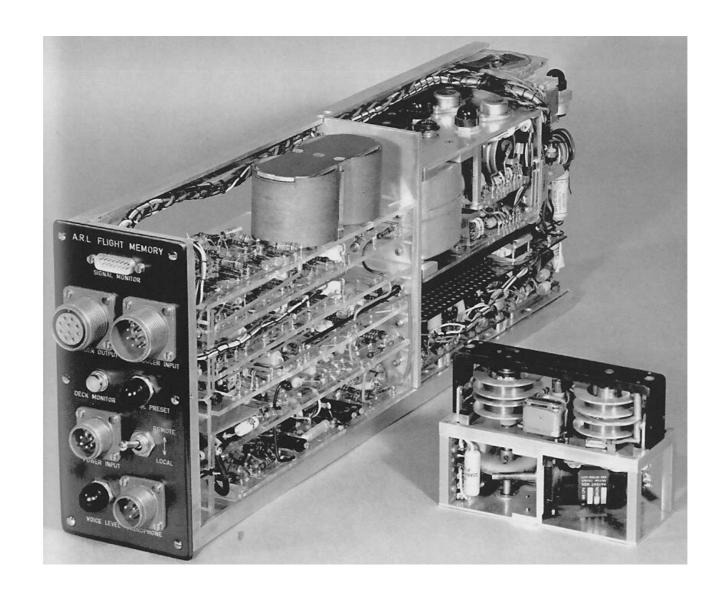

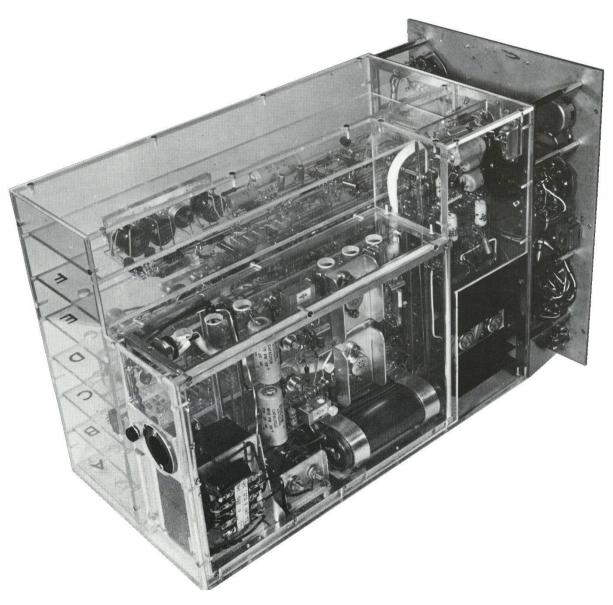

The Electronics Unit comprises (Fig. 7) two major sections, the Signal Processor developed by Mr Sear and the Power System developed by the author. Mr Boswell performed the circuit layout and assembly, and designed the case to house the electronics. A photograph of the Electronics Unit in its case beside the Recorder is shown in Fig. 9. This photograph is of poor quality but is the only one that the author has which carries the Electronics Unit label. A photograph of the Electronics Unit out of its case beside the Recorder is shown in Fig. 10. It bears the sole label ARL Flight Memory which, without the addition of "Electronics Unit" is unfortunate as the Flight Memory system also includes its inputs (cockpit microphone and transducers) and the Recorder to which its output is connected, and the Ground Station Unit.

Descriptions of the Signal Processor and Power Supply sub-sections (Sec. 4.2.2.1 and Sec 4.3) of the Electronics Unit will follow.

#### 4.2.2.1 Signal Processor

The Signal Processor comprises all the elements within the main rectangle in Fig. 7 except the Power System which will be considered later. It has been divided into three sub-sections: Cockpit Voice Signal Processor, Flight Data Signal Processor, and Cockpit Voice and Flight

Data Combination for Recorder (Refer to Sec. 4.2.2.1.1, Sec. 4.2.2.1.2 and Sec. 4.2.2.1.3 respectively).

# 4.2.2.1.1 Cockpit Voice Signal Processor

The Cockpit Voice Signal Processor comprises (Fig. 7) the Pre-Amplifier, High Pass Filter, Clipper and Low Pass Filter. The High Pass Filter and the Low Pass Filter will be considered together as a Band Pass Filter. The Clipper has no effect for normal voice levels and will be considered separately.

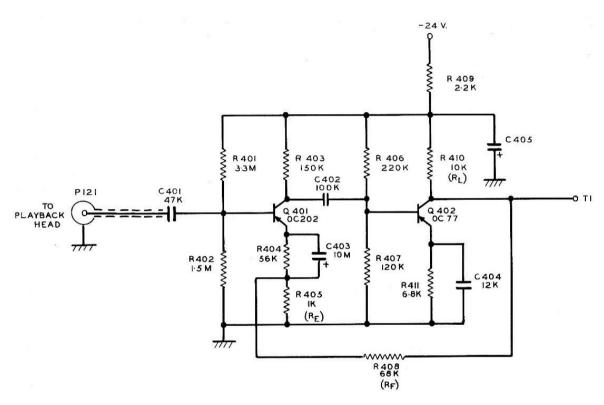

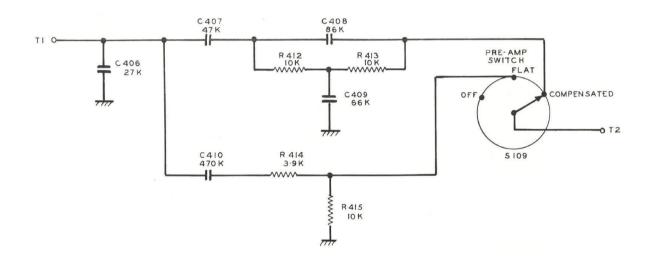

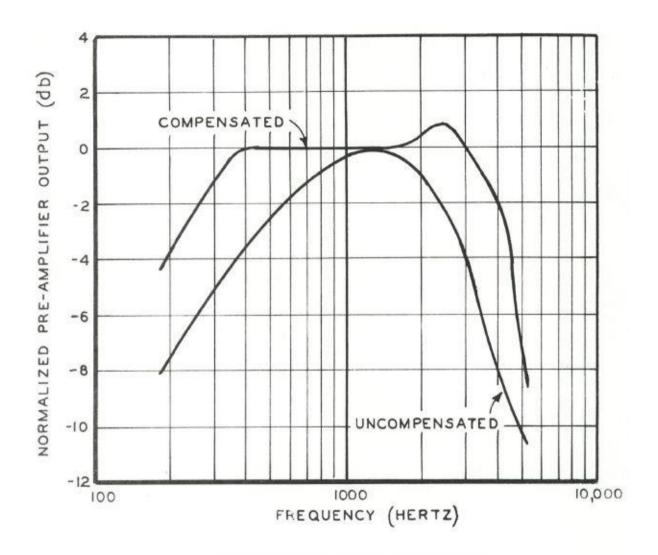

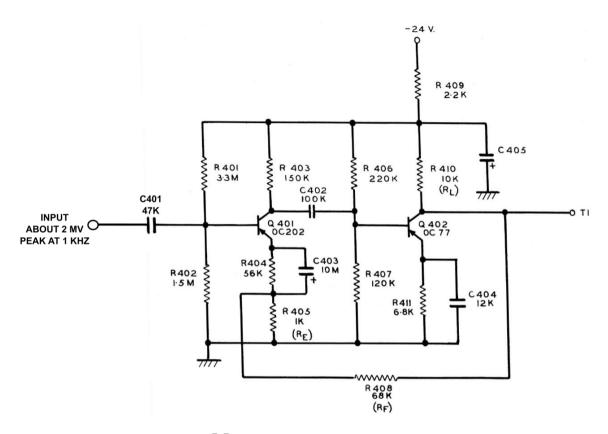

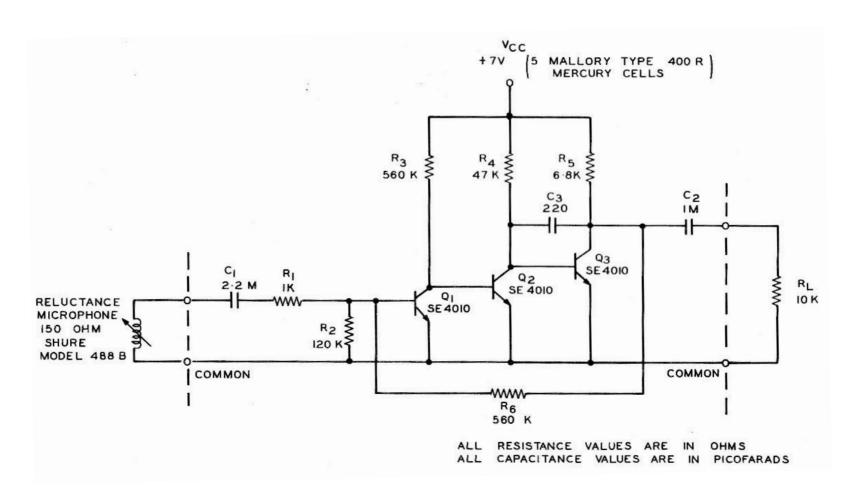

#### 4.2.2.1.1.1 Pre-Amplifier

The author does not have circuit details for this pre-amplifier. It would have been a multi-stage transistor AC amplifier capable of amplifying an input of some millivolts from the microphone to an output in the volt range. Nearly all amplifiers use feedback to stabilise their overall gain. Detailed analysis of amplifiers is not simple. Some further notes on amplifiers and references to documents that provide more detailed analyses of their operation are provided in Appendix 1.

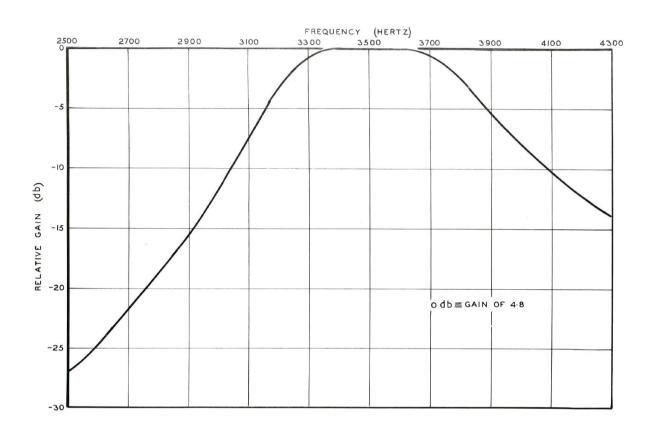

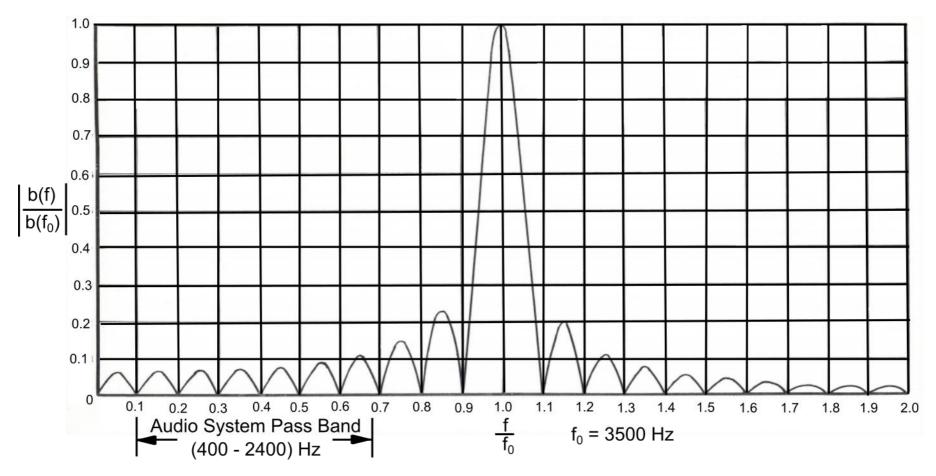

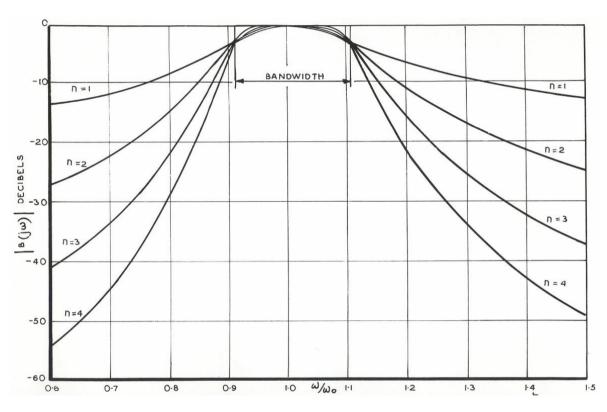

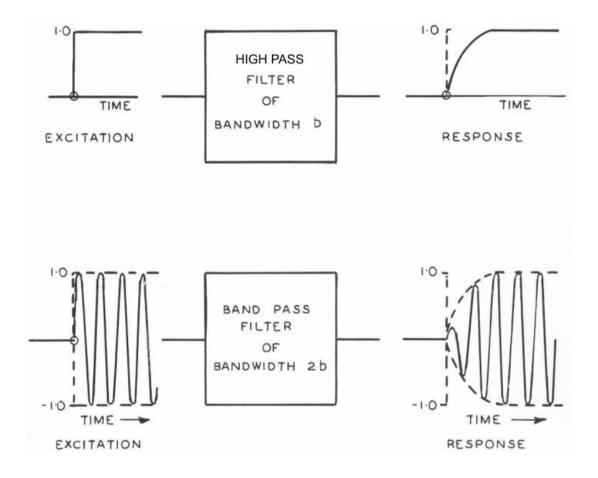

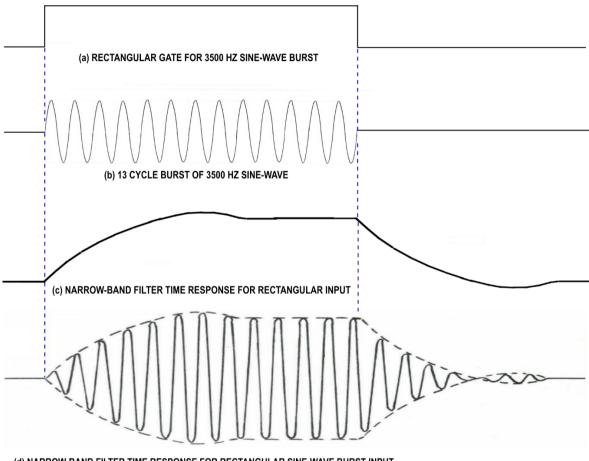

#### 4.2.2.1.1.2 Band-Pass Filter

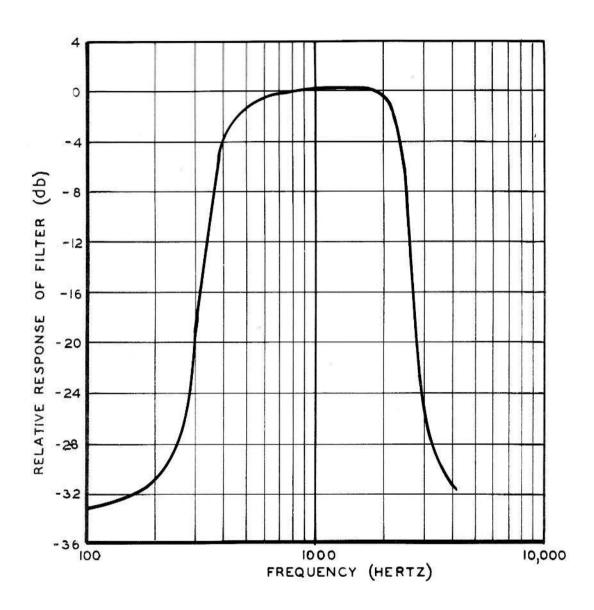

The design requirement for the Band Pass filter was that the upper limit of its pass band be well clear of the Flight Data signal comprising switched bursts of a 3500 Hz sinusoidal signal. The setting of the lower limit of the pass band was somewhat arbitrary but had to be not too high to compromise voice intelligibility. It was also advantageous to attenuate frequencies below about 400 hertz to reduce the amount of aircraft noise which is accentuated at the low frequency end of the spectrum. Cut-off frequencies for the band-pass filter were 400 Hz and 2400 Hz. At the cut-off frequencies, the response is 3 db below that at the mid-band frequency. At 3 db, power is half and voltage is  $1/\sqrt{2}$  (0.7071) of that at mid-band frequency. The ratio of upper to lower cut-off frequencies  $F_U/F_L$  equals 6.0. To achieve that separation a High Pass filter (400 Hz cut-off frequency) and Low Pass filter (2400 Hz cut-off frequency) were required. Which filter is placed closer to the microphone input is insignificant.

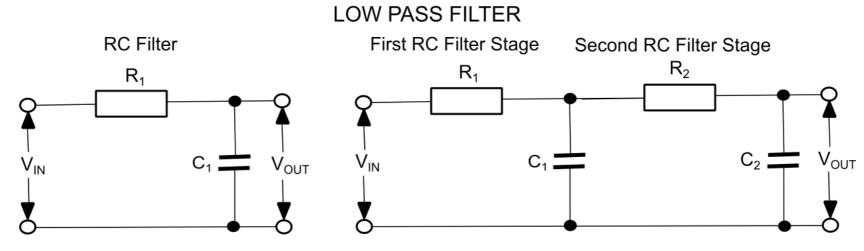

Basic high pass and low pass filters using R (Resistor) and C (Capacitor) components are shown in Fig. 11. Such arrangements, often with amplifier elements as well, are the most commonly used for filters. The key property of capacitors is that they block DC and lower frequency signals but pass high frequency signals readily (i.e. have frequency dependent impedance). Observe how the position of the R and C components are reversed (Fig. 11) for high versus low pass filters. Further information on the characteristics of basic electronic filters including pass band gain, cut-off frequency, phase shift and stop band attenuation slope, is readily available on the web. One such source provides relevant information for a Passive High Pass Filter (Ref. 4), an Active High Pass Filter (Ref. 5), a Passive Low Pass Filter (Ref. 6) and an Active Low Pass Filter (Ref. 7).

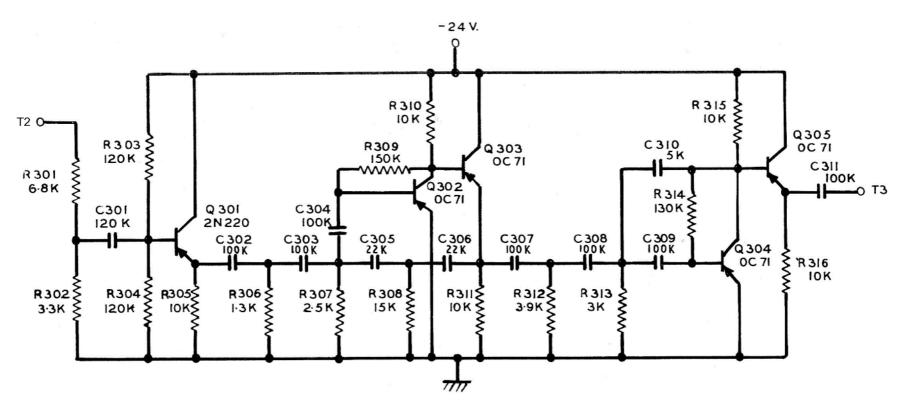

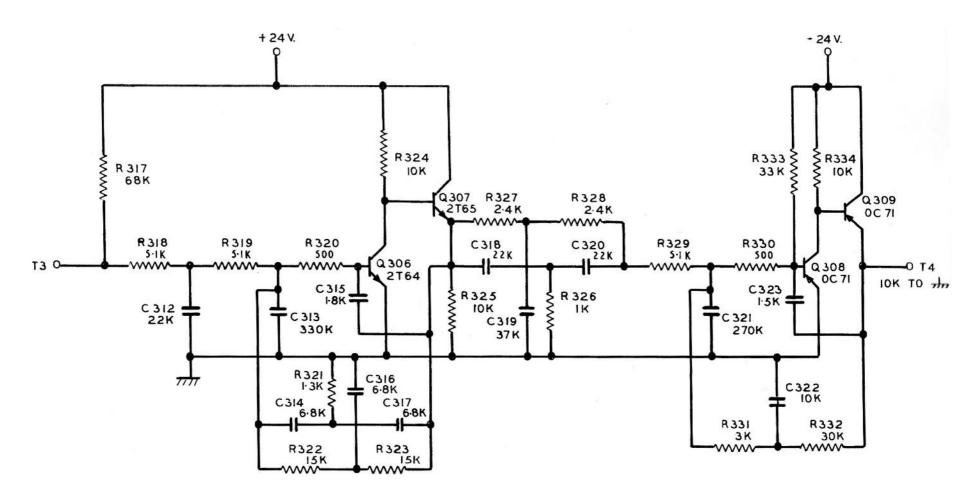

Although the circuit and function details for the Airborne Electronics Unit were never documented the author used the same High Pass and Low Pass Filter circuits for the Ground Station Unit and that was documented (Ref. 8). The High Pass Filter circuit (Fig. 12) is a copy of Figure 9 of the Ground Station document. The Low Pass Filter circuit (Fig. 13) is a copy of Figure 10, and the Band Pass Filter frequency response (Fig. 14) is a copy of Figure 11. For

both circuits, capacitor values are indicated in picoFarad ( $10^{-12}$  Farad) units where K  $\equiv 10^3$ . In more recent times, a 100 K capacitor, for example, would be designated as  $0.1 \,\mu F$ .

The High Pass and Low Pass Filters for the Flight Memory project comprised standard filter circuits which included potentiometers to allow the filters' frequency responses to be adjusted experimentally. Inclusion of the basic R and C circuits is readily observed in the final circuits.

Approximate stop band attenuation slopes in the region below the 3 db cut-off frequency (from about 6 db down) have been deduced in Appendix 2 from the frequency response graph of Fig. 14. The estimate is 39 db per octave for the High Pass Filter and 46 db per octave for the Low Pass Filter. Those figures are indicative of a very high-grade band pass filter.

From the Fig. 14 graph, the attenuation at 3500 Hz (used for the Flight Data Processor) is about 30 db (a factor of 31.6 below the audio filter mid-band 0 db value).

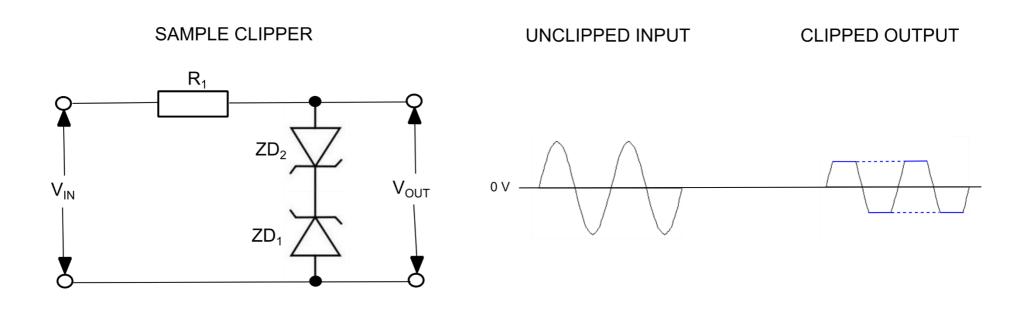

# 4.2.2.1.1.3 Clipper

The author has no details on the circuit that was used to limit the voltage input to the Low Pass Filter (refer to Fig. 7). A sample clipper circuit using Zener diodes is shown in Fig. 15. Clippers are used in many applications and there is nothing special about their use in audio applications. Sound at normal levels is not affected. A Zener diode is a silicon semiconductor device that permits current to flow in either a forward or reverse direction. It has a well-defined reverse-breakdown voltage, at which it starts conducting current, and continues operating continuously in the reverse-bias mode. At the time of the Flight Memory System development Zener diodes were in common use and the author used them as voltage references for the regulated DC supplies for the Airborne Electronics Unit.

For the Fig. 15 clipper the positive clip voltage is the reverse breakdown voltage for ZD<sub>1</sub> plus the forward voltage drop across ZD<sub>2</sub> (typically about 0.7 V). The inverse applies for the negative clip voltage. Normally ZD<sub>1</sub> and ZD<sub>2</sub> would be identical. In that case, if the breakdown voltage for ZD<sub>1</sub> is  $V_B$  and its forward voltage drop is  $V_F$ , then the upward clip voltage would be  $+(V_B + V_F)$  and the downward clip voltage would be

$(V_B + V_F)$ . There may be a need to adjust  $V_{IN}$  (by a suitably chosen voltage divider for instance) if Zener diodes of desired breakdown voltage are not available.

#### 4.2.2.1.2 Flight Data Signal Processor

The author has notes on various configurations for the Flight Data Signal Processor that reveal some minor differences. The configuration that will be adopted in this document is that for which the most information is available. The Flight Data Signal Processor comprises (Fig. 7) the Clock Pulse Generator, Multiplexer, Analog Output Offset Producer, Pulse Duration Modulator, and Sine-Wave Amplitude Modulator.

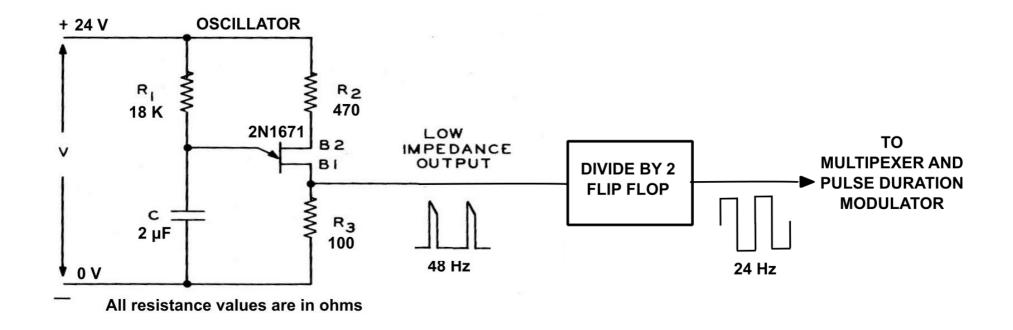

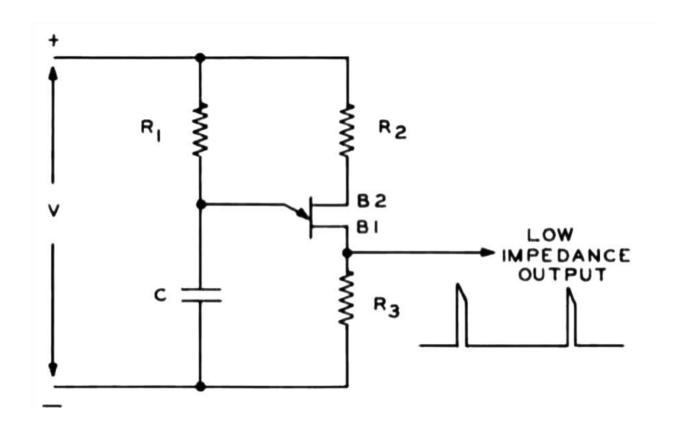

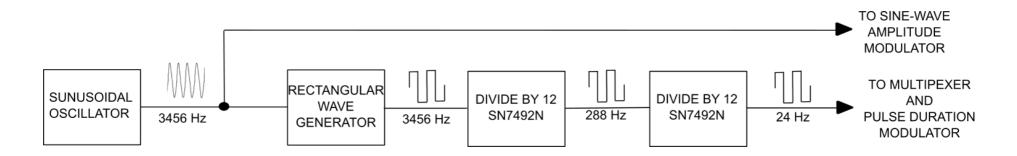

#### 4.2.2.1.2.1 Clock Pulse Generator

The author does not have circuit details for the 24 Hz Clock Pulse Generator (refer to Fig. 7). For the Airborne Electronics Unit Power System (Sed. 4.3) the author had used an RC circuit, unijunction transistor and divide-by-two flip-flop to obtain a rectangular output with equal duration up and down levels. Although the circuit used was for a different frequency output, the requirement for the Clock Pulse Generator was otherwise the same. The circuit shown in

Fig. 16 provides component details for a 24 Hz output signal equivalent to the circuit (Fig. 41) for the 400 Hz output signal used in the Power System except for the capacitor with a different capacitance value.

Adding the suffix 1 to designate the values for the  $R_I$  and C components and the output signal frequency for the 400 Hz version, and suffix 2 for the 24 Hz output version, then if  $R_{I2}$  equals  $R_{II}$  it follows that  $C_2 = \frac{C_1 f_1}{C_2 f_2}$ . For the 400 Hz version  $C_I$  equals 0.12  $\mu$ F, and that gives  $(C_2 = 2.0 \,\mu\text{F})$ . The value  $R_I$  (Fig. 16) equals 18 K is nominal and needs to be trimmed experimentally to provide the 24 Hz signal output. For the 400 Hz version that was achieved using a fixed 15 K resistor in series with an adjustable 5 K resistance trimmer.

The author had some notes on an alternative circuit arrangement that would provide reference signals 24 Hz and 3500 Hz (approximately) from a common source. Details are provided in Appendix 3. The 3500 Hz is required for the Sine-wave Amplitude Modulator (Fig. 7). While the circuit would provide the 24 Hz clock frequency, the carrier frequency for the Amplitude Modulator would be 3456 Hz, slightly less (1%) than the 3500 Hz design value. That difference would be hardly noticeable.

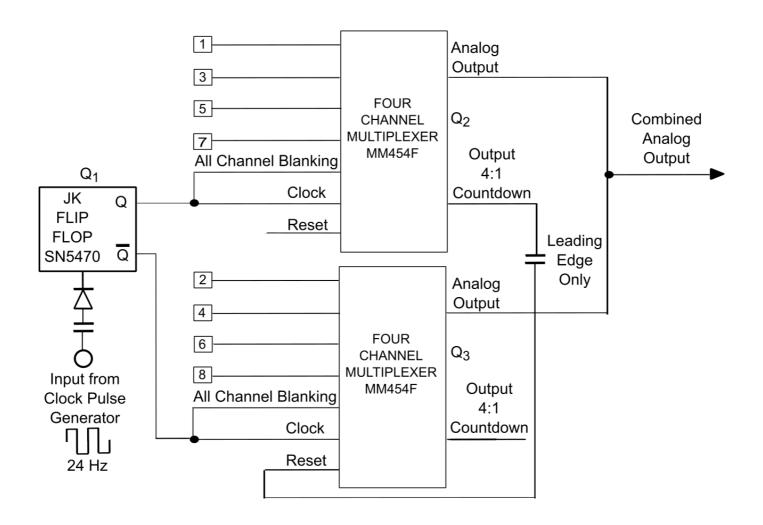

#### **4.2.2.1.2.2** Multiplexer

The Multiplexer circuit shown in Fig. 17 is based on the author's undated hand-written notes. The circuit comprises three semiconductor integrated-circuit components ( $Q_1$ ,  $Q_2$  and  $Q_3$ ) and a few discrete components.  $Q_1$  (SN5470) is a positive-edge-triggered Flip-flop with Preset and Clear. It divides the input clock frequency by 2.  $Q_3$  and  $Q_4$  (both MM454F) are four-channel multiplexers with  $Q_2$  handling odd channels (1, 3, 5 and 7) and  $Q_3$  handling even channels (2, 4, 6 and 8).

The author is not sure this circuit was used in the Flight Data Processor and was unable to confirm that. SN5470 and MM454F integrated-circuit types were available in 1961 when the Mk 2 Flight Memory system was being developed.

#### 4.2.2.1.2.3 Analog Output Offset Producer

If the 5 V transducer output is represented by 100%, then the following apply:

| Input                 | Output |

|-----------------------|--------|

| 5.5 V MARKER (Fig. 7) | 120%   |

| 5 V transducer output | 110%   |

| 0 V transducer output | 10%    |

The Analog Output Offset Producer has two purposes:

- Produce a zero-offset equivalent to 10% of the full scale (5.0 V transducer output) if the zero offset in the PDM is set to zero volt.

- Produce a 10% over-limit to accommodate the MARKER (used mainly for channel synchronization during Ground Station Flight Data recovery). That would mean producing 5.0 V output for a 6.0 V input if the zero offset in the PDM were set to zero volt, or to producing 5.0 V output for a 5.5 V input if the zero offset were performed in the PDM.

The required zero offset can be provided as detailed here or via the adjustment available in the PDM. In either case there is a need to limit the PDM input signal to 5 V maximum. An analysis of an emf (electromotive force) and resistor network that would be suitable for producing the required analogue voltage input to the PDM is provided in Appendix 4. By setting the zero-adjustment-leg open-circuit, the zero-adjustment-within-the-PDM option can be adopted.

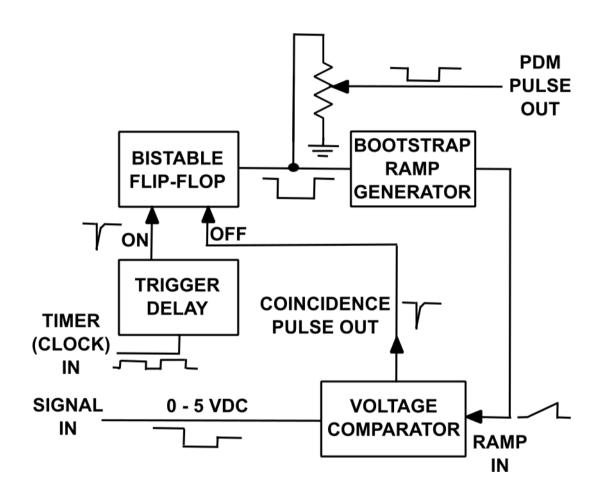

#### 4.2.2.1.2.4 Pulse Duration Modulator (PDM)

#### Overview

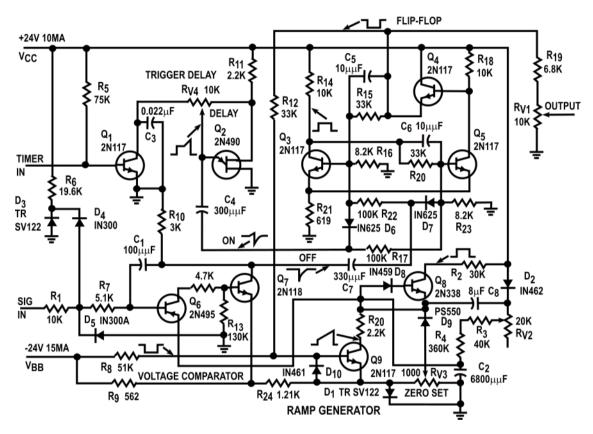

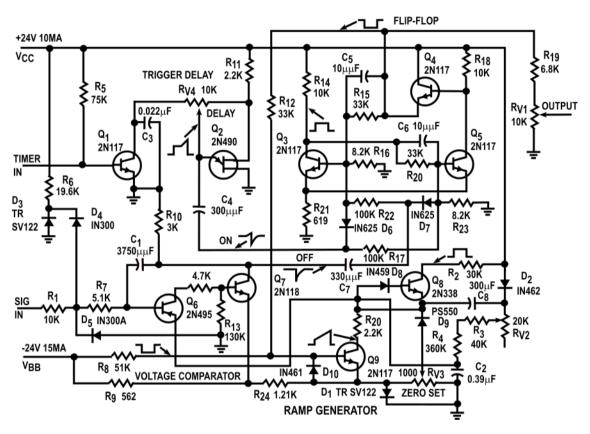

The Flight Memory PDM circuit is based on a 1958 Electronics Engineering article (Ref. 9) for a Telemetry Keyer which used a sampling rate of 900 readings per second and a signal input range of 0 to 5 V. That meant some changes were required for the Flight Memory application which used a 24 readings per second sampling rate and a nominal 5.5 V analogue input signal range (if the zero-signal offset were included in the PDM circuit). In the document currently being written, PDM is used in lieu of Keyer as that terminology better describes its function and is more recognizable by the electrical engineering and scientific communities. There is no record available (to the author) on what changes were incorporated. Fig. 18 is a block schema of the PDM and it is valid for both 900 and 24 Hz versions. Circuit details for the 1958 Telemetry Keyer are provided in Fig. 19. While most of the important components had labels (e.g. Q<sub>1</sub> to Q<sub>8</sub> for transistors, R<sub>2</sub> etc. for some resistors and C<sub>1</sub> etc. for some capacitors), other components were unlabelled. To facilitate the functional description of the PDM's operation, labels have been added to all those components that did not have them in the original circuit. C<sub>1</sub>, which was used for two different components in the original circuit, has been expanded to C<sub>1</sub> and C<sub>2</sub>.

There is no written record of the Flight Memory PDM circuit. The author can confirm that all transistors are the same as those used in the 900 Hz version. All diodes, except D<sub>3</sub> and D<sub>1</sub> (both SV122 Zener diodes), are silicon types which, when conducting, will have a nominal voltage drop of 0.7 V. The author could not find any details on D<sub>3</sub> and it is assumed that device is no longer in production. According to Ref. 9, "Zener diode D<sub>3</sub> is used for a 5 V reference". It is assumed that it is a 5.1 V Zener diode (standard type available) that will clip any input signal in excess of 5.8 V (adding D<sub>3</sub> and D<sub>4</sub> voltage drops). Use of D<sub>3</sub> would be unsuitable for an input signal in excess of 5 V.

The required pulse width output for the Flight Memory System is known from the settings for the Sine-Wave Amplitude Modulator (Fig. 7) to be reviewed in a later Section. The required pulse durations are indicated in the following table.

| Analog input           | Number of 3500 Hz cycles | Pulse duration (msec) |

|------------------------|--------------------------|-----------------------|

| 0 V transducer minimum | 10                       | 2.86                  |

| 5 V transducer maximum | 110                      | 30.56                 |

| 5.5 V MARKER channel   | 120                      | 34.29                 |

The period of the 24 Hz Timer (Clock) input is 1/24 sec which equals 41.67 msec. That provides a minimum gap of 7.38 msec or 17.7% of the Timer (Clock) period.

The block schema (Fig. 18) indicates the modulator comprises four distinct elements:

| 1 | Trigger Delay            |

|---|--------------------------|

| 2 | Bootstrap Ramp Generator |

| 3 | Voltage Comparator       |

| 4 | Bistable Flip-Flop       |

While element 1 has no input from the three other elements, elementss 2, 3 and 4 are very much inter-related. These elements will be examined next, mainly in terms of what does and what does not need to be changed relative to the 900 Hz Keyer.

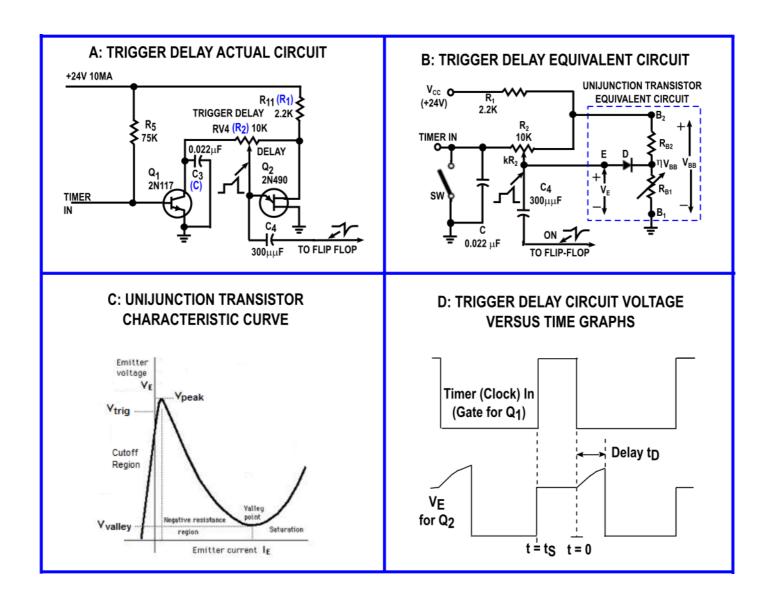

# Trigger Delay

The purpose of the Trigger Delay circuit is to provide a delay from the time at which the multiplexer switches to a new channel to the time at which the analogue input is interrogated. This ensures the analogue input has stabilised before its value is measured. The Trigger Delay circuit comprises  $Q_1$ ,  $Q_2$  and associated components (in Fig. 19).

For zero signal from the Timer  $Q_1$  is saturated and  $Q_2$  is drawing no emitter current. If a negative-going gate is applied from the Timer input,  $Q_1$  is driven to cut-off allowing capacitor C to charge. As its voltage rises so does the voltage on the delay-adjustment resistor  $R_2$ . At a certain instant emitter current will be drawn from the unijunction transistor  $Q_2$ . As the emitter of  $Q_2$  draws current the base current of  $Q_2$  drops very rapidly and its emitter voltage drops to zero.

The input impedance of  $Q_1$  is low (42 ohm approximately). Hence for zero signal in, the base current of  $Q_1$  is about 24/75 mA (0.32 mA).

Analysis of the operation of the Trigger Delay circuit is much more complex than those for the other three PDM elements. The author found some of his hand-written notes (undated but probably written in 1961) on the derivation of the magnitude of the time delay. A copy of that analysis with some extensions is provided in Appendix 5.

The Appendix 5 analysis determined that about 60% adjustment of the  $R_{V4}$  potentiometer provided trigger delay adjustment in the approximate range (0 to 211  $\mu$ s). For the remaining 40% adjustment of R, unijunction transistor  $Q_2$  will be switched on and its emitter grounded (0 V). Ref. 9 indicated that 100  $\mu$ s delay was used for the 1958 Telemetry Keyer. That value should also have been suitable for the Flight Memory PDM as the analogue input stabilisation time is mainly a function of such times for the Flight Data Processor's switching devices and external transducers. These times would be similar for the 900 Hz Keyer and the 24 Hz Flight Memory applications.

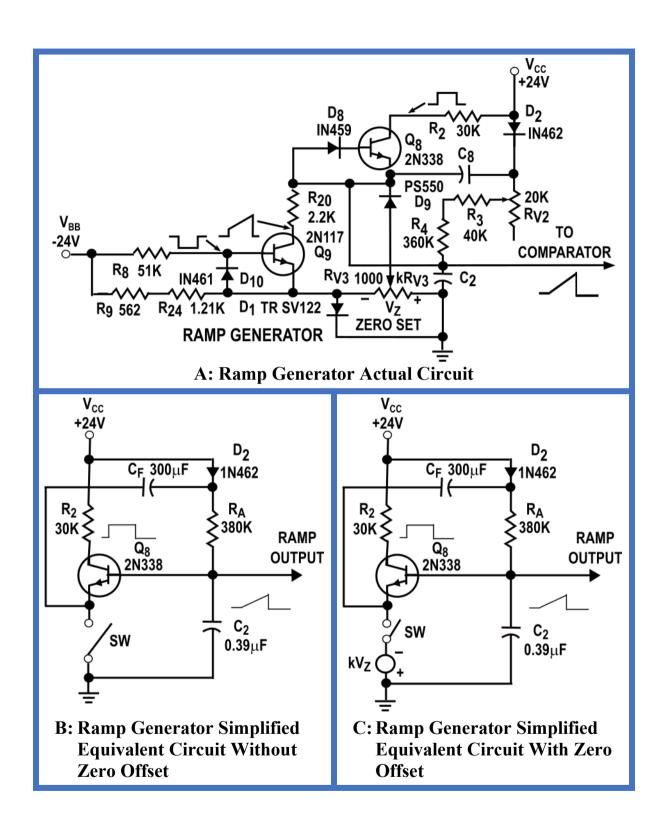

# Bootstrap Ramp Generator

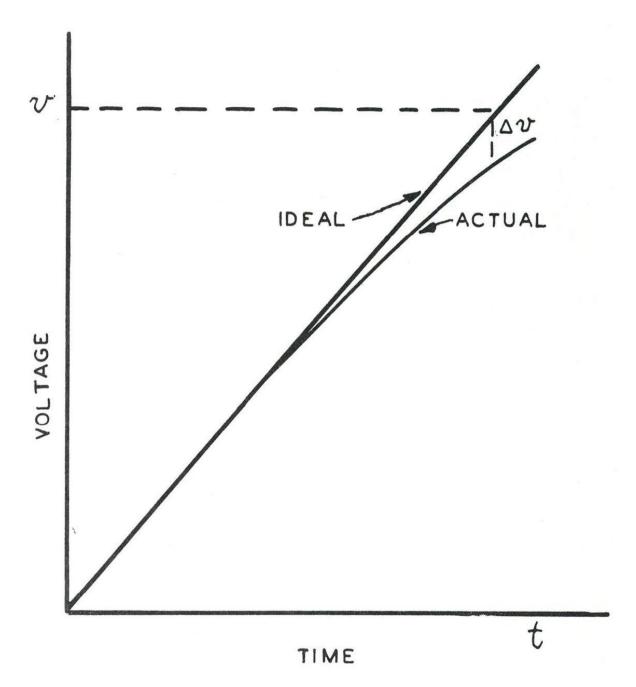

A perfect ramp generator is one for which its slope is constant over the period of interest. The voltage versus time and current relationship for a capacitor is well known. It is given by:

$$\frac{dv}{dt} = \frac{i}{C}$$

where C is the capacitor's capacitance in Farad, i is the instantaneous current through the capacitor in Amp and  $\frac{dv}{dt}$  is the instantaneous rate of voltage change (volt per second). By

creating a circuit which sets i constant, the requirement to set  $\frac{dv}{dt}$  constant would be achieved. To highlight the constant current, the instantaneous i in the above equation will be replaced with capital I as shown below.

$$\frac{dv}{dt} = \frac{I}{C}$$

The actual ramp generator circuit is shown in Fig. 20A and simplified equivalent circuits for without and with internal zero offset are shown in Fig. 20B and Fig. 20C respectively. A zero offset is essential and hence Fig. 20B is applicable where the zero offset is arranged external to the PDM. Arranging the zero-offset external to the PDM is the simpler approach particularly as there is a need to restrict the maximum input signal to no greater than 5V and adding the zero-offset adds no extra complexity as indicated in Sec. 4.2.2.1.2.3.

Irrespective of which zero offset option is used, the PDM output pulse duration will be equal to the ramp signal duration. For no internal zero offset in the PDM, ramp capacitor  $C_2$  will be fully discharged (voltage drop across it is equal to zero) when the ramp is inactive (PDM output is high). Also, transistor  $Q_9$  and its equivalent switch SW will be in the ON state when the PDM output is high.

Proper operation of the ramp generator requires bootstrap capacitor C<sub>F</sub> to rapidly charge to  $(V_{CC} - V_D)$ , where  $V_D$  is voltage drop across diode  $D_2$  when switch SW (Fig. 20B) is closed and retain this DC voltage drop when SW is opened. For  $(V_{CC} = +24V)$ , and  $(V_D = 0.7V)$ , the DC voltage drop across  $C_F$  will be 23.3V. The current into the ramp capacitor C<sub>2</sub> will be the current through R<sub>A</sub> minus the base current into Q<sub>8</sub>. As indicated in Ref. 9, the base current for Q<sub>8</sub> should remain constant for the duration of the ramp. For this analysis it will be assumed that the base current through Q<sub>8</sub> is negligible. With that assumption the current through C<sub>2</sub> will equal the current through R<sub>A</sub>. For the current through R<sub>A</sub> to be constant, the voltage drop across it must remain constant. To achieve this the AC ramp component voltage must also appear at the C<sub>F</sub>-to-D<sub>2</sub> junction. As soon as the ramp voltage across C<sub>2</sub> begins to rise, diode D<sub>2</sub> will cease to pass current and bootstrap capacitor C<sub>F</sub> will provide the current for R<sub>A</sub>, and C<sub>F</sub> will act as a short circuit for the AC ramp voltage which will appear at each end of C<sub>F</sub>. The value of C<sub>F</sub> must be large enough to retain its DC voltage drop during ramp generation but not so large that replacement of any lost charge (assumed to be small) during ramp generation cannot be rapidly achieved. A suitable value for C<sub>F</sub> is the value used in the original keyer application multiplied by the ratio of original sampling rate to that for the Flight Memory application.

$$C_F = 8 \text{ x } (900/24) \ \mu\text{F} = 300 \mu\text{F}$$

The effect of the inclusion of the zero offset will now be considered. If  $D_1$  (Fig. 20A) were a standard silicon diode it would be reverse-biased and the voltage drop across  $R_{V3}$  would be:

$$\frac{V_{BB} R_{V3}}{R_9 + R_{24} + R_{V3}} = \frac{-24 \times 1000}{562 + 1210 + 1000} V = -8.66 V$$

However, D<sub>1</sub> is a Zener diode with breakdown voltage of 5.1 V (presumably as indicated earlier). The above calculation verifies that the breakdown condition would apply. While the operation of the actual zero offset circuit (Fig. 20A) is difficult to comprehend, it can

be radically simplified as shown in Fig. 20C. When switch SW is closed the emitter of  $Q_8$  will be set to  $-kV_Z$  (refer to Fig. 20A) and that approximate value will also be transferred to ramp capacitor  $C_2$ . In practice,  $kR_{V3}$  would be adjusted experimentally to provide the required zero offset. The following would apply for the "Internal-to-PDM" and "External-to-PDM" zero offset options.

| Zero offset option | Initial voltage across ramp capacitor C <sub>2</sub> | Voltage across bootstrap capacitor C <sub>8</sub> |

|--------------------|------------------------------------------------------|---------------------------------------------------|

| Internal-to-PDM    | $-kV_{Z}$                                            | $V_{CC} - V_D + kV_Z$                             |

| External-to-PDM    | 0                                                    | $V_{CC} - V_{D}$                                  |

The next step is to calculate the required capacitance value of  $C_2$  for the Flight Memory application. Recalling the basic relationship between ramp slope  $\frac{dv}{dt}$ ,  $C_2$  charging current and the  $C_2$  capacitance value, the following applies.

$$I = M$$

, where  $\left(M = \frac{dv}{dt}\right)$  and is assumed to be constant.

Let  $V_X$  be the DC voltage drop across bootstrap capacitor  $C_8$ . It will be the same when transistor  $Q_8$  is ON and when it is OFF. The charging current I, for ramp capacitor  $C_2$  is given by:

$$I = \frac{V_X}{R} = MC_2$$

$$M = \frac{V_X}{RC_2}$$

The pulse duration equals the ramp duration, and assuming a perfectly linear ramp, M can be calculated for any ramp duration but it is convenient to do so for its longest duration (i.e., for MARKER). First consider the options detailed in the following table.

#### PDM Internal Offset Table

| Calibration | EXT OFFSET | Transducer        | INT OFFSET   | MARKER   |

|-------------|------------|-------------------|--------------|----------|

|             | Fixed      | Signal Range      | Fixed        | Fixed    |

|             | $V_{ZB}$   | Variable $v_{TA}$ | $V_{ZA}$     | $V_{SA}$ |

| 100%        | 0% (None)  | 0% to 100%        | 100% to 110% | 120%     |

| 4.545 V     | 0.00 V     | 0.00 to 4.545 V   | 0.455 V      | 5.00 V   |

#### PDM External Offset Table

| Calibration | EXTt OFFSET | Transducer        | INT OFFSET | MARKER   |

|-------------|-------------|-------------------|------------|----------|

|             | Fixed       | Signal Range      | Fixed      | Fixed    |

|             | $V_{ZB}$    | Variable $v_{TB}$ | $V_{ZA}$   | $V_{SB}$ |

| 100%        | 10%         | 10% to 110%       | None       | 120%     |

| 4.167 V     | 0.417 V     | 0.417 to 4.583 V  |            | 5.00 V   |

The INT and EXT Zero voltage offsets are slightly different (5.0/11 = 0.4545) versus (5.0/12 = 0.4167) respectively. The difference (5/11 - 5/12 = 5/132) represents 0.758 % of full-scale input voltage (5.0 V) difference.

The pulse duration  $T_S$  for the MARKER signal is 34.29 ms and must be the same for INT and EXT zero offset settings.

$$M = 5.00/34.29 = 0.1458 \text{ volt/ms}$$

$$M = \frac{V_x}{RC_2}$$

V<sub>X</sub> has different values depending on whether the zero offset is performed within the PDM or external to it. Suffix A will be added for the former and B for the latter.

$$V_{XA} = +V_{CC} - V_D + kV_Z = 24 - 0.70 + 0.4545 = 23.7545$$

volt

$V_{XB} = +V_{CC} - V_D = 24 - 0.70 = 23.3$  volt

$(RC)_A = \frac{V_{XA}}{M} = \frac{23.7545}{0.1458} = 162.92$  ms

$(RC)_B = \frac{V_{XB}}{M} = \frac{23.3}{0.1458} = 159.81$  ms

If  $(R = 410 \text{ K})$ , then  $C_{2A} = 0.397 \text{ } \mu\text{F}$  and  $C_{2B} = 0.389 \text{ } \mu\text{F}$

$C_A$  and  $C_B$  are close to being the same. Setting ( $C_2 = 0.39 \mu F$ ) and trimming the adjustable R value to set pulse duration to its correct value, would be appropriate.

When the Zero Offset is provided internal to the PDM, the required value is  $V_Z$ , where  $V_Z$  is the breakdown voltage for Zener diode D<sub>1</sub> (Fig. 20A). As shown above,  $kV_Z$  equals 0.4545 V. As  $V_Z = 5.1$  V, (k = 0.095) which is about 10% of the adjustable range for  $R_{V3}$ . Replacement of  $R_{V3}$  (1000 ohm) with 820 ohm (fixed) in series with a 200 ohm variable resistance would have been more appropriate for the Flight Memory application.

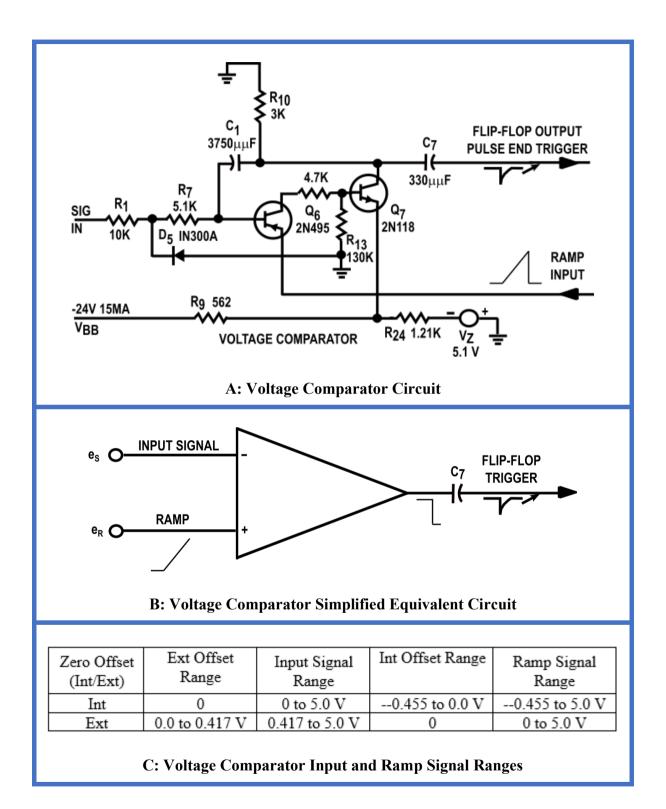

#### Voltage Comparator

The voltage comparator circuit is shown in Fig. 21A. It is powered from the  $V_{BB}$  (-24V) supply. It has two input signals:

- 1. SIG IN (Fig. 19) comprising a scale-adjusted multiplexer output plus a zero offset if the external zero offset option applies.

- 2. The output from the ramp generator.

For convenience the above signals have been given the designation  $e_S$  and  $e_R$  respectively.

For any multiplexer channel, it can be assumed that  $e_S$  remains constant for the full clock period (1/24 sec) and will have a maximum value of 5.0 V for the MARKER channel. The ramp generator output  $e_R$  will have a start-value of zero volt or close to that value if the internal zero offset option is in use.

The over-voltage clipper (Fig. 19) sets a clip voltage equal to the breakdown voltage of Zener diode  $D_3$  plus the ordinary conducting voltage of silicon diode  $D_4$ . The clip voltage has been excluded from the voltage comparator considered here (Fig. 21A) as it represents an open circuit at all times for within-range  $e_S$  signals. The voltage comparator is a Schmitt

trigger circuit. For  $(e_R < e_S)$ ,  $Q_6$  is reverse biased (non-conducting). The input impedance loading for  $e_S$  is very high and further increased via feedback capacitor  $C_I$ . The size of this capacitor would need to follow an inverse relationship to the sampling rate.  $C_I$  for the 900 Hz Keyer had a value of  $100\mu\mu$ F and so a value of  $3750\mu\mu$ F approximately would be suitable for the Flight Memory application.  $Q_7$  is actively biased while  $Q_6$  is switched off. For  $(e_R < e_S)$ , the output of  $Q_7$  will have a high value. When  $(e_R = e_S)$  the emitter of  $Q_6$  will become forward-biased. At that instant  $Q_6$  will switch on and the output of  $Q_7$  will drop sharply. The output of the voltage comparator is AC coupled via  $C_7$  to the FLIP-FLOP and provides its Output-Pulse-End-Trigger. The  $330\mu\mu$ F value for  $C_7$  used for the 900 Hz Keyer should also be suitable for the Flight Memory application.

A simplified equivalent circuit for the voltage comparator is shown in Fig. 21B. It shows a high-gain inverting amplifier with relevant signal waveforms. When  $(e_R < e_S)$  the output is high and when  $(e_R > e_S)$  it is low with an abrupt changeover when  $(e_R = e_S)$ ..

The table in Fig. 21C summarises the Input Signal  $e_S$  and Ramp Signal  $e_R$  voltage ranges according to whether the zero offset is performed internal-to or external-to the PDM.

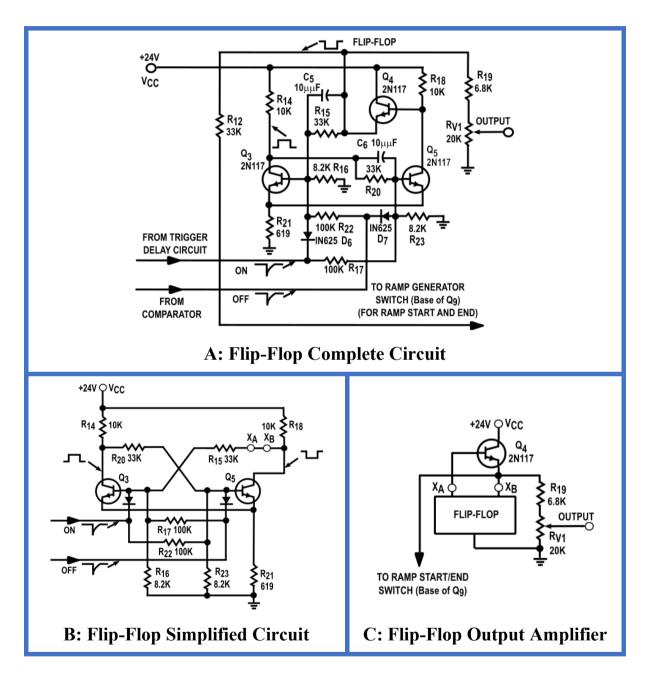

#### Flip-Flop

The complete Flip-Flop circuit is shown in Fig. 22A. Transistors  $Q_3$  and  $Q_5$  are used in a conventional edge-triggered flip-flop arrangement and  $Q_4$  in a unity gain output amplifier. It is helpful to consider the flip-flop and the output amplifier as separate entities as indicated in Fig. 22B and Fig. 22C respectively.

The output amplifier connects to the flip-flop between points  $X_A$  and  $X_B$  (Fig. 22B). In that figure  $X_A$  and  $X_B$  are joined together and that is a close approximation for the effect of the output amplifier on the operation of the flip-flop. The symmetry of the flip-flop is obvious when the flip-flop is drawn as shown in Fig. 22B. ON and OFF voltage triggers are connected to the base terminals of  $Q_3$  and  $Q_5$  respectively via diodes which guarantee that only the negative portions of the edge triggers are received by  $Q_3$  and  $Q_5$ . Both triggers produce momentary switch-off of  $Q_3$  and  $Q_5$  respectively. Reinforcement via feedback resistors  $R_{20}$  and  $R_{15}$  resistors ensure that the switch-off states of  $Q_3$  and  $Q_5$  respectively are maintained. The pattern of high (H) and low (L) states of  $Q_3$  and  $Q_5$  are summarised in the following table.

| Condition | Collector Q <sub>3</sub> | Collector Q <sub>5</sub> |

|-----------|--------------------------|--------------------------|

| Before ON | Н                        | L                        |

| After ON  | L                        | Н                        |

| After OFF | Н                        | L                        |

The output amplifier (Fig. 22C) is a Common Collector (Ref. 10) type. Its gain (emitter voltage divided by base voltage) is close to 1. Input and output voltages are in phase, input impedance is high and output impedance is low. This means there is negligible loading on the input signal source and the amplifier's output "sees" a much higher impedance than the actual load value that would apply for an amplifier without feedback stabilised gain. Final output voltage is adjustable in the range 0 to 75% of  $Q_4$  emitter voltage via the  $R_{19}$  and  $R_{V1}$  voltage divider.

# Complete PDM Circuit for Flight Memory Application

Some changes relative to the 900 Hz modulator (Fig. 19) were required for the 24 Hz Flight Memory application. No changes to semiconductor or resistor components were deemed necessary. Also, no changes were required to capacitors which performed edge triggering operations. It was necessary to change the values of three capacitors ( $C_2$  and  $C_8$  for the Ramp Generator, and  $C_1$  for the Voltage Comparator). New values are ( $C_1$  = 3750  $\mu\mu$ F), ( $C_2$  = 0.39  $\mu$ F) and ( $C_8$  = 300  $\mu$ F). While the capacitor values are theoretically correct, in practice capacitor values would be trimmed experimentally to meet requirements. Circuit details for the 24 Hz Flight Memory PDM are shown in Fig. 23.

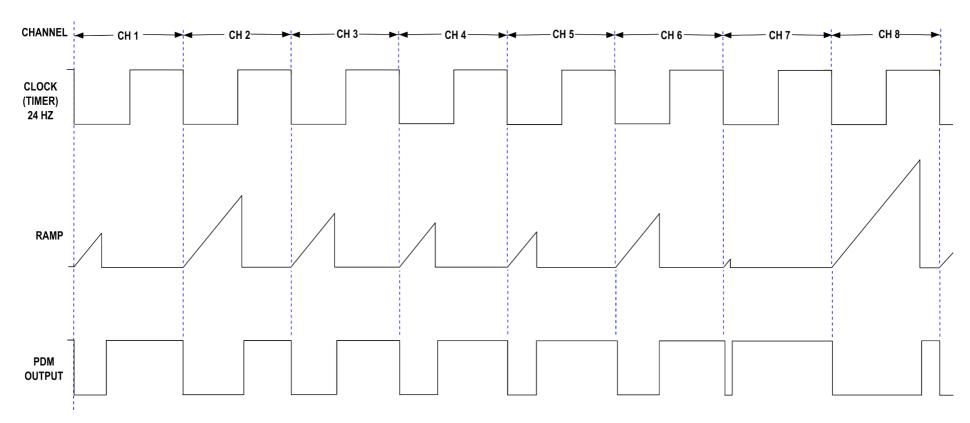

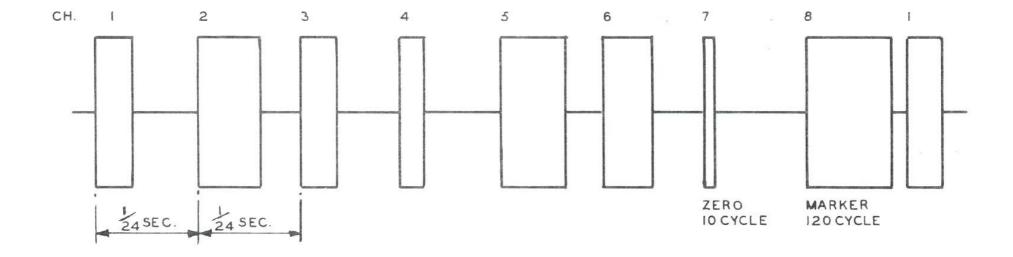

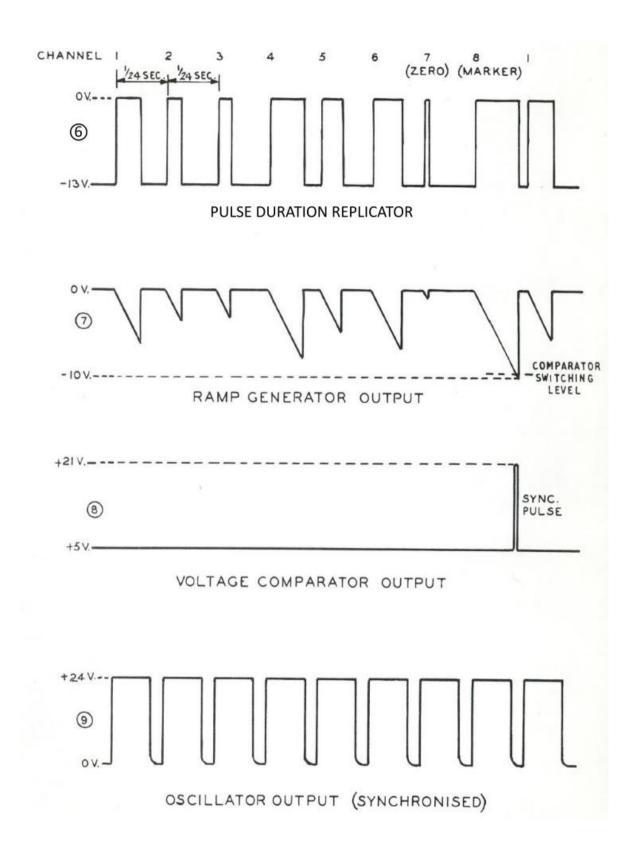

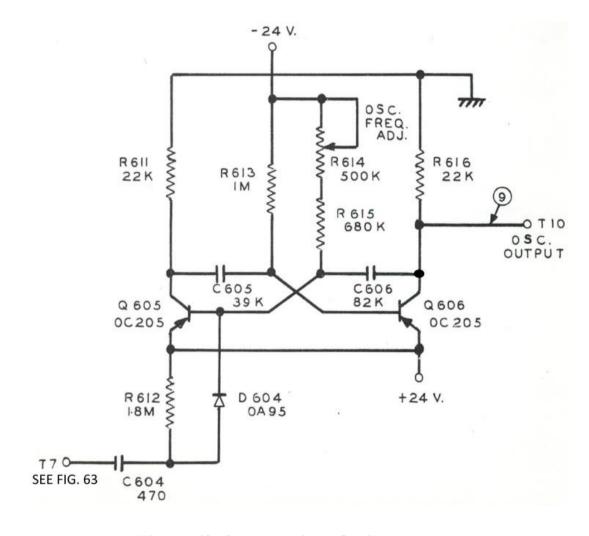

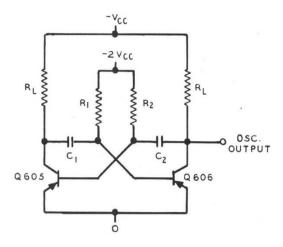

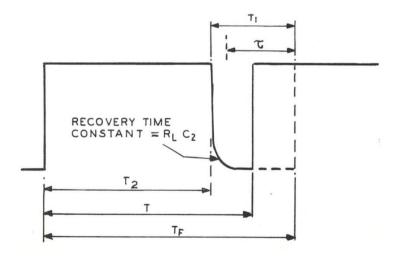

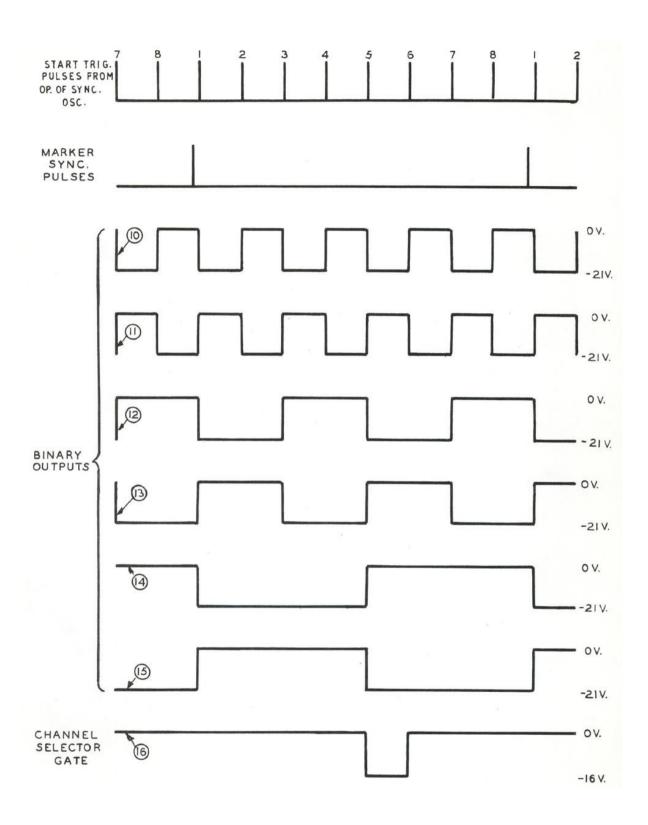

Voltage versus time graphs for one input scan cycle (eight channels) relevant to the PDM are shown in Fig. 24. The 24 Hz Clock (Timer) is shown with equal low and high periods but any other low to high ratio could be used. The essential requirement is that the high-to-low transitions are separated by exactly  $\frac{1}{24}$  second. For the Flight Memory application, the ramp durations for CH 7 (Zero) and CH 8 (MARKER) are invariant. Because the MARKER duration is the duration of 120 cycles of a 3500 Hz sine-wave carrier, and the Zero is  $\frac{1}{12}$  of that, it should be possible to delegate CH 1 to an additional transducer channel. The ramp durations for CH 1 to CH 6 have been set to arbitrary values in Fig. 24.

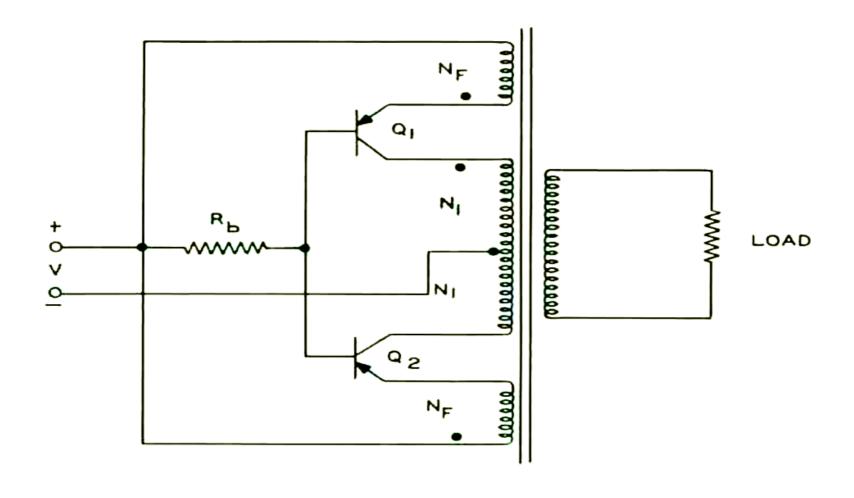

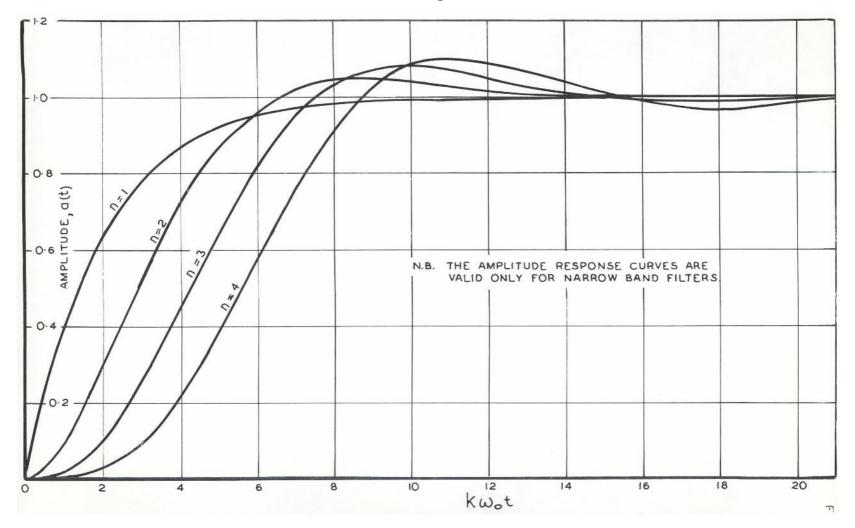

#### 4.2.2.1.2.5 Sine-Wave Amplitude Modulator

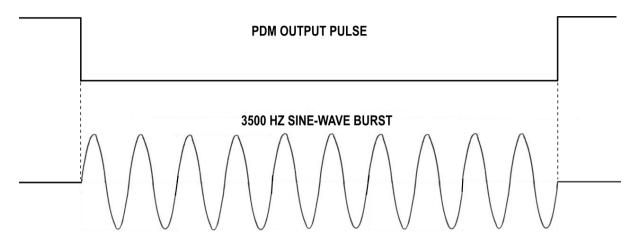

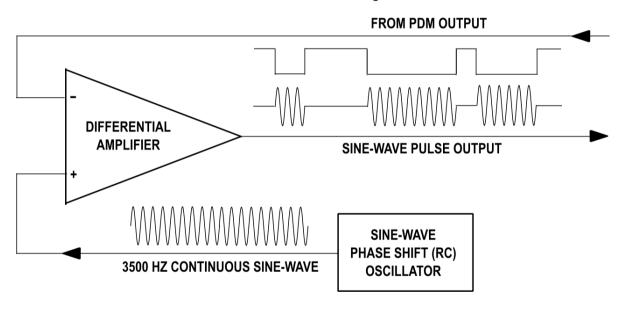

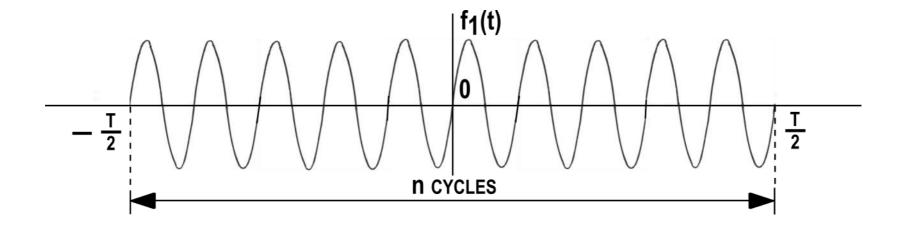

The Sine-Wave Amplitude Modulator (Fig. 7) has a single input which is the PDM's output. It produces bursts of 3500 Hz sine-waves that coincide with the periods for which the PDM output is low. The author has no details of the electronic circuit that was used to perform this function.

What is known is that the sine-wave burst started at full amplitude as illustrated in Fig. 25A. The author is unsure of what happened at the trailing end of the burst. The author has been unable to find a reference to a circuit that would instantly reach full magnitude sine-wave oscillation on receipt of a control signal. Jimenez (Ref. 11) describes a gated oscillator which starts without delay but the oscillator is not sinusoidal.

An equivalent circuit for a Phase-Shift (RC) oscillator (Ref. 12) with gated on/off control is shown in Fig. 25B. This circuit represents a conventional method for producing a gated oscillator output. It employs a sine-wave oscillator with continuous output coupled to a gating signal input (the PDM output). While the idealized sine-wave bursts are shown in Fig. 25B, in practice there will be irregularities for the first couple of cycles and some add-on after the trailing edge of the PDM gate signal. The inherent filtering of the recording and reproducing processes will mean that the sharp transitions of the sine-wave bursts will not be retained.

Because the sine-wave bursts were not band-pass filtered prior to recording, some unwanted signals could be transferred to the audio band. Such unwanted signals will be considered in the next section.

#### 4.2.2.1.3 Cockpit Voice and Flight Data Output Generator

This item has two elements: the Combiner and the Current Output Amplifier with the latter providing the signal that is passed to the Magnetic Wire Recording Deck. These elements are shown in the Fig. 7 block schema.

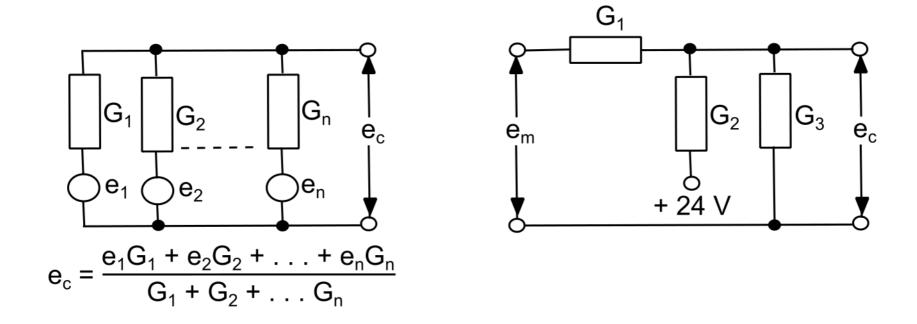

#### 4.2.2.1.3.1 Combiner

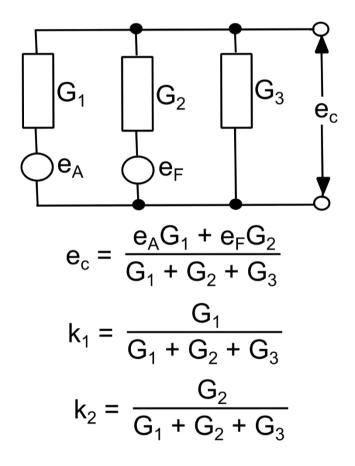

The Combiner (Fig. 7) combines Cockpit Voice and Flight Data signals into a single output for which the two items are separated by frequency. The author has no details of the circuit that was used. A simple resistance network is the usual approach and it is assumed to be what was used. Appendix 4 and Fig. A4 provide a general analysis for an n-emf system. The analysis is simplified by using conductance in lieu of resistance. A simplified equivalent circuit is shown in Fig. 26A and the actual circuit is shown in Fig. 26B.

Defining Cockpit Voice audio input as  $e_A$ , Flight Data input as  $e_F$  and the Combiner output as  $e_C$ , the following equation applies:

$$(e_C = k_1 e_A + k_2 e_F)$$

where  $k_1 = \frac{G_1}{G_1 + G_2 + G_3}$  and  $k_2 = \frac{G_2}{G_1 + G_2 + G_3}$

If each conductance is replaced with its inverse resistance the following apply:

$$k_1 = \frac{R_2 R_3}{R_1 R_2 + R_2 R_3 + R_1 R_3}$$

and  $k_2 = \frac{R_1 R_3}{R_1 R_2 + R_2 R_3 + R_1 R_3}$

if  $R_1 = R_2$  and  $R_3 \gg R_1$ , then  $k_1 = k_2 \approx 0.5$

Such an approximation would apply if  $(R_1 = R_2 = 15K)$  and  $R_3 = 150K$ .

It is assumed that the Output Amplifier (Fig. 7), to which the Combiner output is connected, has very high input impedance due to feedback (it is assumed to have unity voltage gain).

The author performed a Fourier analysis (Ref. 13 p3) of a pulsed sinusoidal voltage mainly in support of the design of the filter for the Ground Unit's Flight Data recovery. An extension of that analysis in Appendix 6 shows that the pulsed sine-wave signal  $e_F$  for the Flight Data signal has residual components within the pass-band of the Cockpit Voice signal. That combined with a small proportion of the Flight Data signal passed by the audio filter during ground system data recovery was responsible for the presence of a regular undefined audio signal (of relatively low volume) that could be heard when no voice signal was present on the recorded audio channel. The author has no record of that signal. The author likened the extraneous sound to that of the Australian Mole Cricket insect's song and that is also elaborated upon in Appendix 6. It was concluded that eliminating the problem would have been straight forward once its cause was established.

A high pass filter inserted between the Sine-Wave Amplitude Modulator and the Combiner (Fig. 7) would have resolved the problem. Since the Flight Memory Electronics system never proceeded to commercial production, no further development took place after the 23 March 1962 flight validation test. Hence the problem remained unresolved.

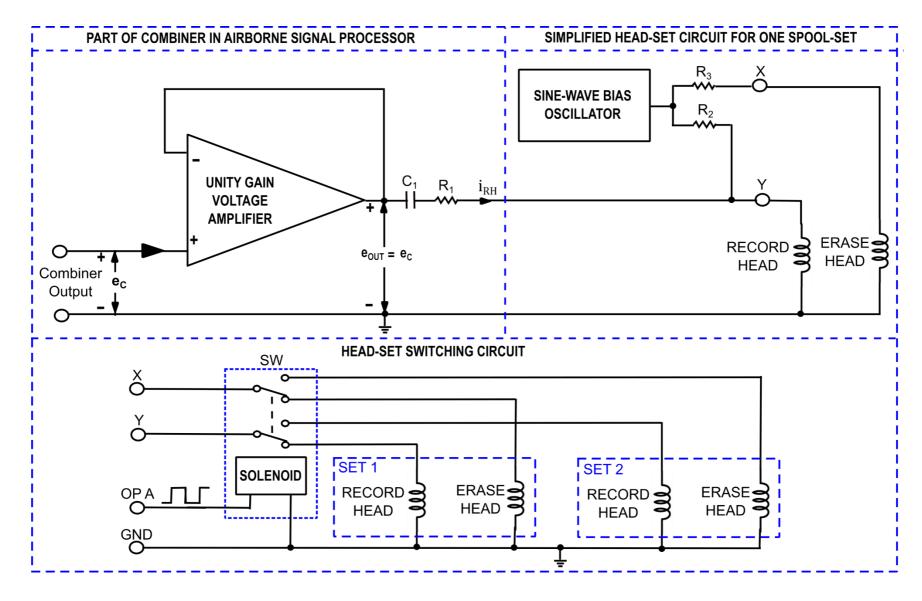

#### 4.2.2.1.3.2 Combined Signal Recording

The following recording-related actions were required:

- 1. Provide a high frequency erase signal for the erase-head to remove any pre-recorded signal from the wire before it passes the record-head.

- 2. Provide a high frequency inaudible sine-wave (bias) signal to be added to the record-head signal to improve recording quality.

3. Provide record-head signal current unaffected by frequency-dependent record-head impedance.

The high frequency signal for 1 and 2 can be the same. For tape recorders it is generally in the 40 to 150 kHz range (the author used 55 kHz in a different tape-recording application – Ref. 14) and the requirement for magnetic wire recording would probably be similar. Ref. 15 has a block diagram showing the erase-head signal and the record-head bias signal as being the same, and record and playback using the same head. That arrangement matches that for the Flight Memory system recording and playback.

The author has no details for the actual circuit that was used for the Flight Memory system erasing and recording. A simplified circuit that would meet the Flight Memory recording requirement is provided in Fig. 27.

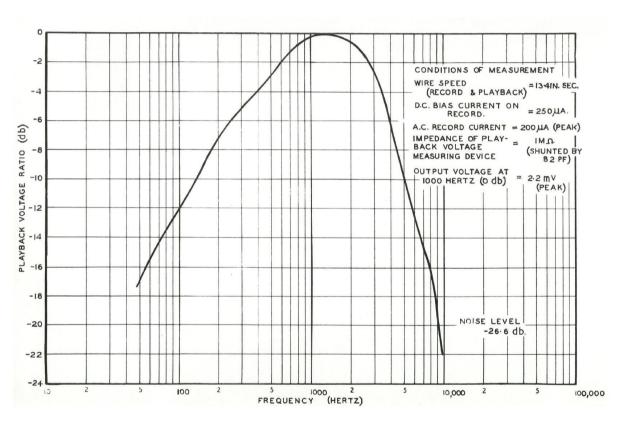

The same head was used for both airborne system input signal recording and output signal playing hack for the ground recovery system. Fortunately, the author made some measurements on the head characteristics that were relevant not only for playing back but also for recording. The relevant information is provided in Ref. 8 (Figure 3). The magnitude of the bias current was indicated as 250  $\mu$ A DC (should have been indicated as AC and the author will assume it was a peak value). The AC record-current was indicated as 200  $\mu$ A peak (assumed to be the 100% signal value). To obtain the required record-head signal current ( $i_{RH}$ ), resistance value of R<sub>1</sub> would need to be made much higher than the impedance value of the record-head over the frequency range of interest (400 to 4000 Hz approximately). Capacitor C<sub>1</sub> would be used as a DC blocker and its impedance over the frequency range of interest would need to be much lower than the R<sub>1</sub> resistance value.

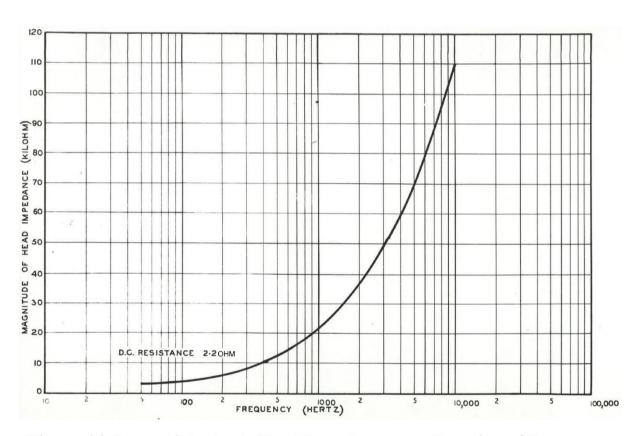

The record/playback head impedance as a function of frequency was plotted in Ref. 8 (Figure 4). There was a labelling error in that figure. The vertical axis marked as KILOHM should have been OHM and likewise the DC resistance should be 2.2 OHM. From the corrected figure, the record/playback head impedance at 4 KHz equals 600 ohm. If L represents the record-head inductance and f the frequency, then the record-head impedance would be equal to  $2\pi fL$ . Using  $(2\pi fL = 60 \text{ ohm at 4 KHz})$ , gives (L = 2.4 mH milliHenry) which is a reasonable value for a record-head inductance.

For a 100% record-head current  $i_{RH}$  of 200  $\mu$ A, and for a nominal value of 5 V peak for  $e_c$ , (Fig. 27), (R<sub>1</sub> = 25 K) would apply. A value of 1.0  $\mu$ F would be suitable for C<sub>1</sub>.

The simplified recorder input schema (Fig. 27) shows the amplifier as a unity gain voltage type. That arrangement agrees with handwritten notes the author made around 1961, but a higher gain amplifier could have been used. The use of unity gain minimises the amplifier output impedance but, with a load of about 25 K, a very low output impedance is not a requirement. A gain stabilised amplifier by feedback is the main requirement.

The sine-wave oscillator (Fig. 27) would provide high frequency erase-head current and record-head bias current. The simplified circuit at the upper right of Fig. 27 shows an arrangement for one of the two erase-and-record head-sets.

The "Head Set Switching Circuit" (Fig. 27) shows a method of providing the required electronic circuit switch-over from one spool-set to the other. OP-A is the same signal (Fig. 6)

that operates one of the trip-switch triggered magnetic clutches for the recorder. OP-B (Fig. 6) is the inverse of OP-A and could be used if a reverse-order switching were required. A nominal 24 VDC solenoid-operated 2-pole change-over switch performs the required spool-set switch-over. When a high signal is applied, the solenoid would activate its switch and when low it would return to its inactive (opposite) switch state.

According to Dr Warren (Ref. 3 p10) who details Design Considerations for the Mk 1 Recorder, "All record of the flight would be erased during taxi-in". The author presumes a similar intention would apply for the Mk 2 Recorder. The proposed automatic erasing would be far from simple and, even if it were realizable, it would be practical for only short duration flights. The author is sure this proposal never proceeded to a test or implementation stage. Post-flight manual erasing by ground support staff would appear to be required to accommodate long duration flights.

If it could be assumed that, by some means, every new flight were to start with the spools containing fully erased magnetic wire and the spools were positioned such that recording always started where spool A was just about to engage its End-Of-Wire trip switch (Fig. 5), then a major design simplification would apply. There would not be a requirement for recording to continue from where it was at the time of the successful landing for the previous flight.

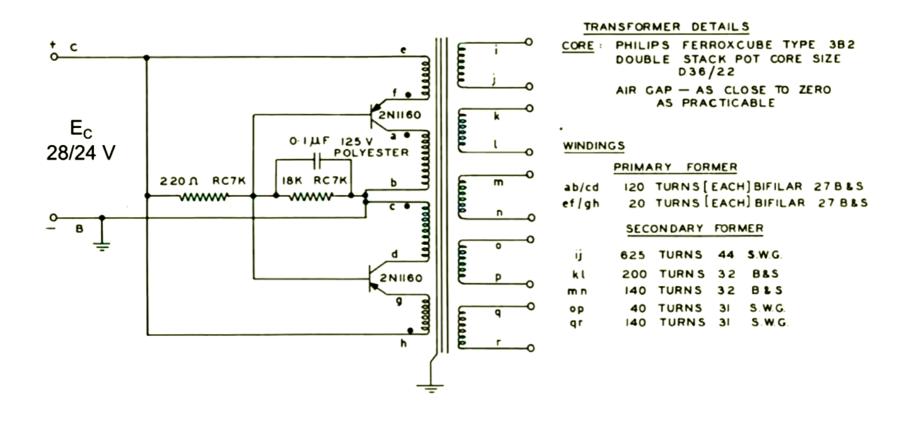

# 4.3 Airborne Power System

The two major requirements of the Power System were to:

- Provide DC power for the Electronics Unit, Transducers and Recorder.

- Provide AC Power for the Recorder motor.

Detailed design information for the Power System is provided in Ref. 16 which was written by the author whose responsibilities included the provision of the Airborne Power System. Complete details of the Power System design are provided in the above referenced document which is in PDF format and can be readily viewed on-line. The main aim of the following subsections is to provide a summary of functions, analyses and circuits for the power system.

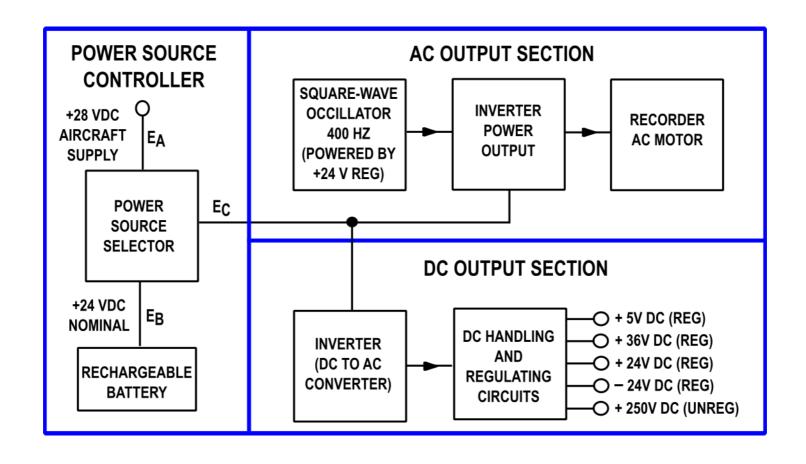

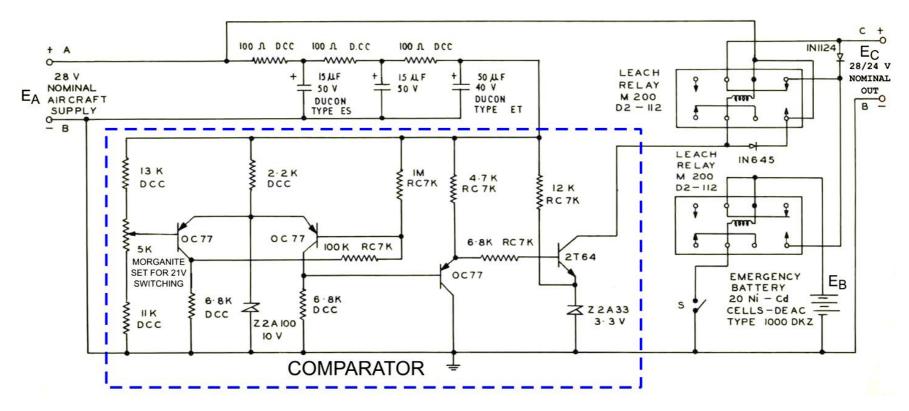

#### 4.3.1 Overview

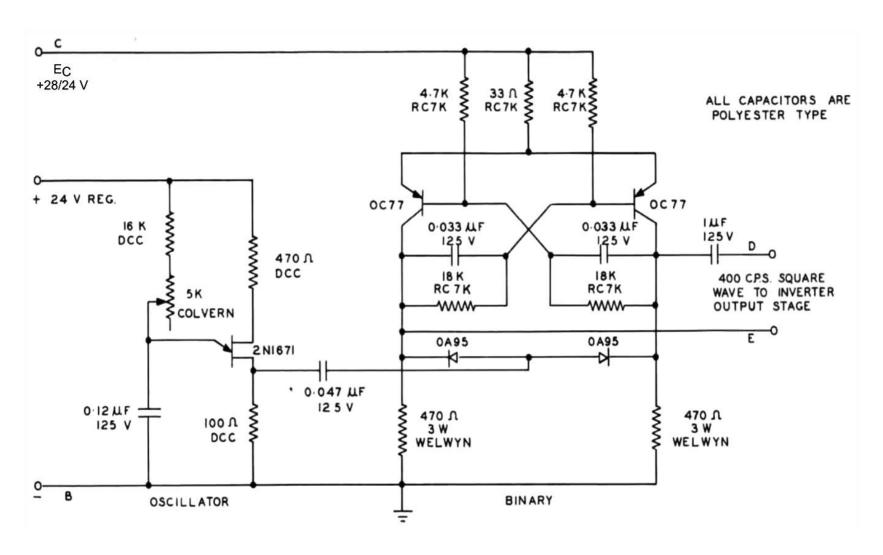

At a high level ARL staff meeting (Appendix 7) it was decided that an emergency battery would be included in the airborne system to allow recording to continue if an electrical power failure occurred during flight. That decision had a major impact on the Airborne Power System development as the simplest solution was to derive both normal and power-loss-emergency power from DC sources. The chosen setup was to derive normal power from the aircraft 28 VDC supply and the emergency power from a rechargeable 24 VDC battery supply. The other standard aircraft supply (200 VAC inter-phase 400 Hz) would have provided a simpler implementation if no emergency battery back-up had been required.

A simplified block schema of the Power System is included in Fig. 7. An extended block schema of the Power System is shown in Fig. 28. The complete Power System, including the emergency battery pack, was installed in the Airborne Electronics Unit.

Three transformers were included in the power system (one in the DC output section and two in the AC output section). All transformers were designed in-house and used cores that were available at the laboratory.

Primary emf sources are given an E designation ( $E_A$  for standard aircraft 28VDC supply,  $E_B$  for the Flight Memory 24VDC emergency battery supply, and  $E_C$  for the switched output which is normally equal to  $E_A$  but in the extremely rare event of an aircraft 28VDC failure it would be equal to  $E_B$ ).

#### 4.3.2 Power Source Controller

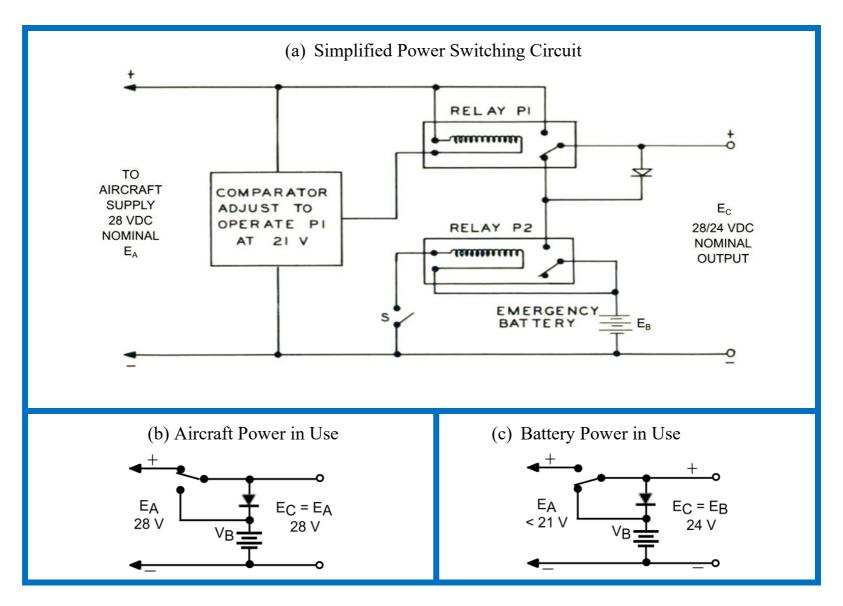

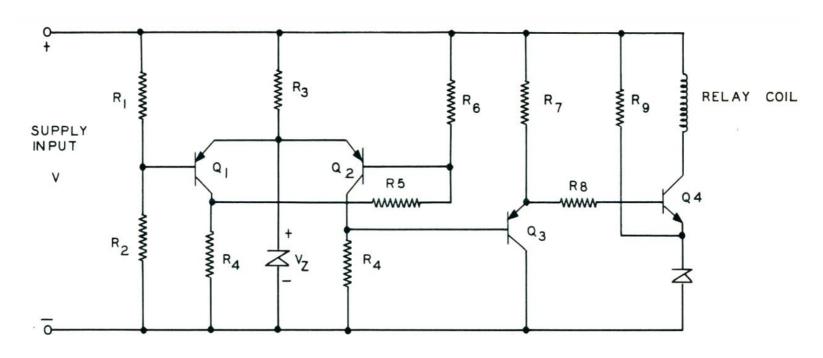

A simplified circuit for the Controller is shown in Fig. 29a (which is a copy of Ref. 16 Figure 1). Relay switching, which provides a simple means of controlling amps (if required) of output current with milliamps of coil current, is used. Relay P1 provides single-pole-changeover switching and P2 is the same as P1 although in that case on-off switching is all that is required. The comparator (to be described below) will energise P1 if the aircraft supply voltage exceeds 21 V and will abruptly de-energise P1 if aircraft supply drops below 21 V (an indication of aircraft 28 VDC failure).

Provided switch S is closed, relay P2 will remain energised both when aircraft supply is normal and if and when aircraft power fails. Simplified circuits Fig. 29b and Fig. 29c show arrangements which would have applied for normal and emergency operation. During normal operation the diode allows charging current from the aircraft supply to pass to the battery but prevents any discharge back into the aircraft supply. If switch S is closed and the aircraft supply is switched off, the emergency battery will provide power to the recording system and hence discharge. It is therefore essential that switch S be opened after a normal landing. The general requirement that the recording system be installed on a "fit and forget" basis rules out the possible solution that the pilot manually operates switch S. One possible solution would be for switch S action be provided by a connection to the weight-on-wheels (WOW) switch in common use in relation to aircraft undercarriage operation.

The battery cells in use were Nickel-Cadmium sintered plate type with a nominal cell voltage of 1.2 V. The battery pack comprised 20 such cells giving a nominal pack voltage of 24 V.

The comparator switch shown in block form in Fig. 29a uses a Schmitt trigger circuit. The P1 and P2 relays used are miniature military-qualified type M200 manufactured by Leach Corporation. These relays are a 2-pole-changeover type with only one pole in use for the Flight Memory application. The relay contacts are rated at 2 A resistive. To energise the 600 ohm coils in these relays about 18 V maximum is required. The drop-out voltage is in the vicinity of 5 V.

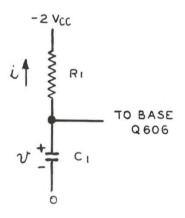

The basic form of the comparator circuit is shown in Fig. 30 (which is a copy of Ref. 16 Figure 3). At low levels of input voltage V, with Zener diode  $V_Z$  not conducting,  $Q_1$  will be "on" and  $Q_2$  will be "off", provided that  $\left(\frac{R_2}{R_1} < \frac{R_4}{R_3}\right)$ . When  $\left[V = \left(1 + \frac{R_3}{R_4}\right)V_Z\right]$ , the Zener diode will conduct and hold the common emitter point fixed relative to the negative supply line.  $Q_1$  will continue to conduct until reverse bias appears on its emitter-base junction. This will occur when  $\left[V = \left(1 + \frac{R_1}{R_2}\right)V_Z\right]$ . At this level of input voltage, the Schmitt circuit will change state, with  $Q_2$  switching "on" and  $Q_1$  "off". A positive going step of voltage approximately  $V_Z$  volt in magnitude will appear on the collector of  $Q_2$ . This pulse is fed via emitter follower  $Q_3$  to transistor  $Q_4$  which acts as a switch. The low breakdown voltage Zener diode in the emitter

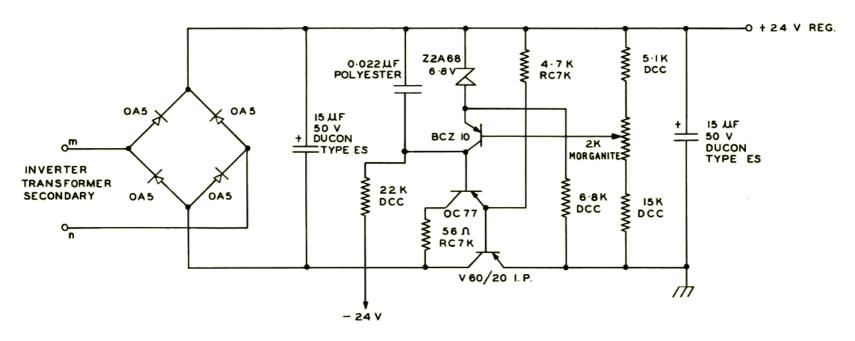

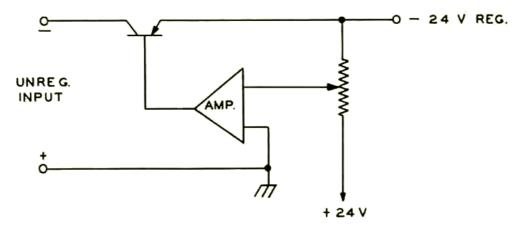

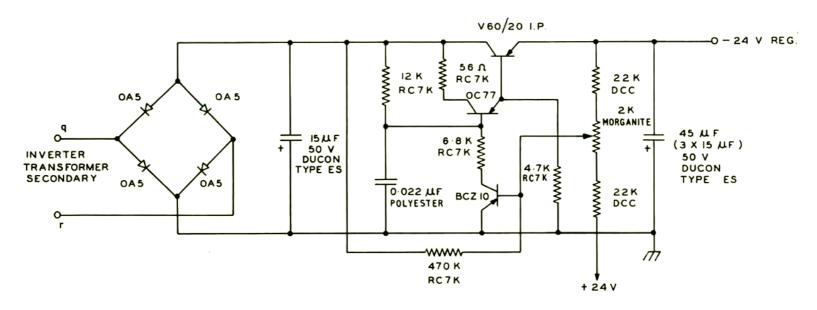

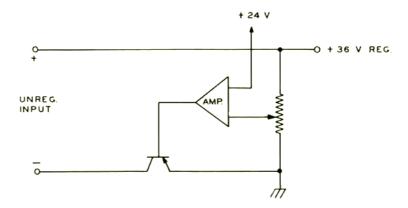

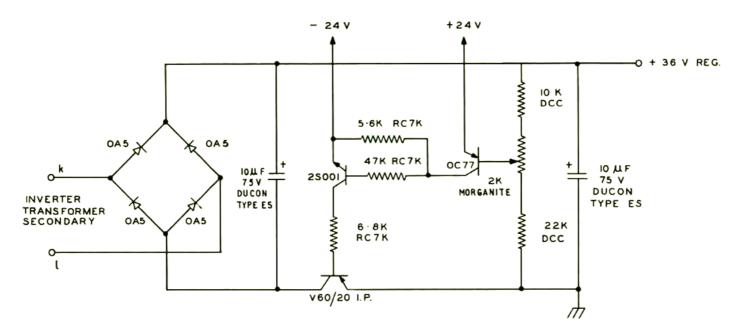

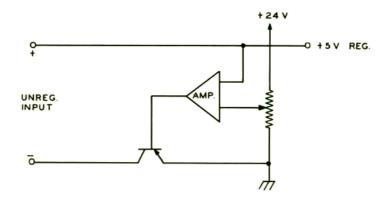

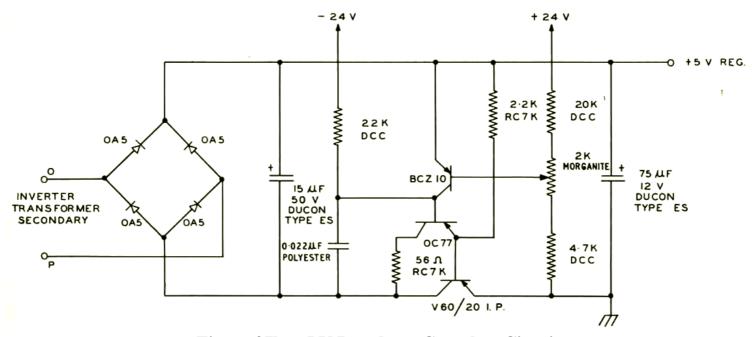

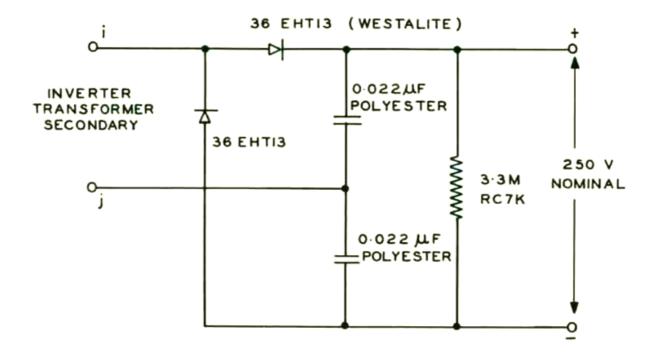

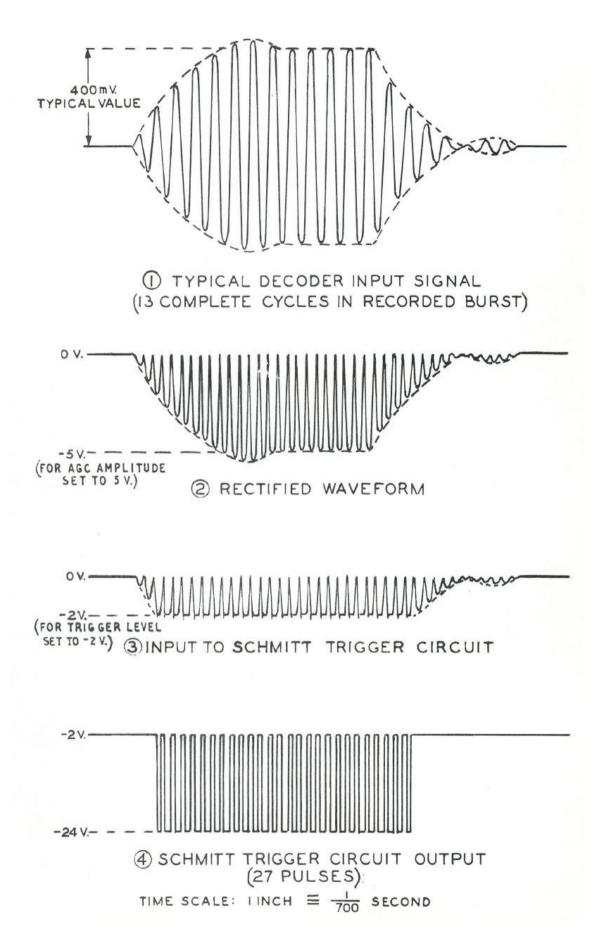

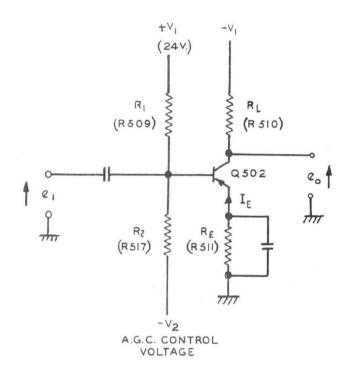

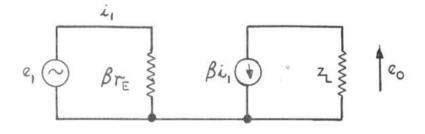

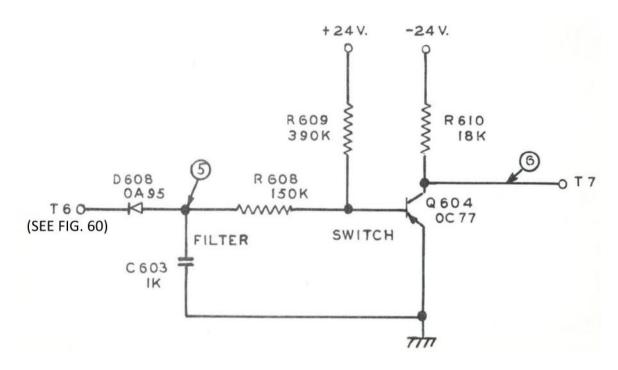

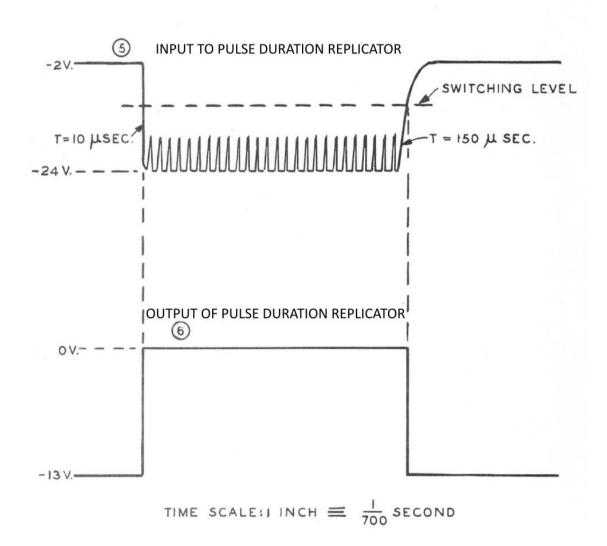

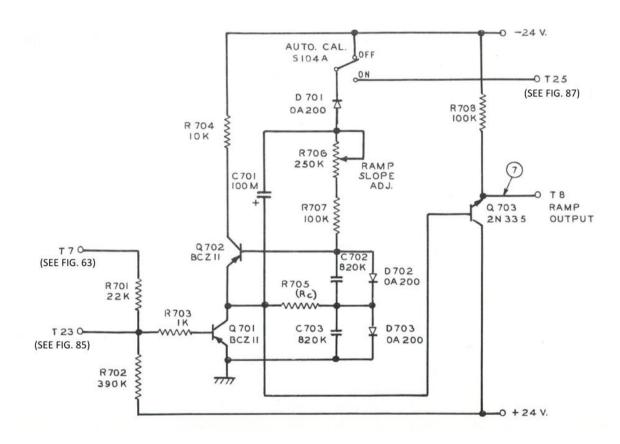

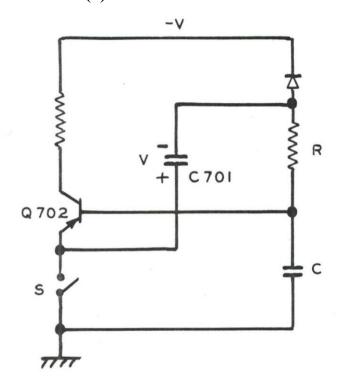

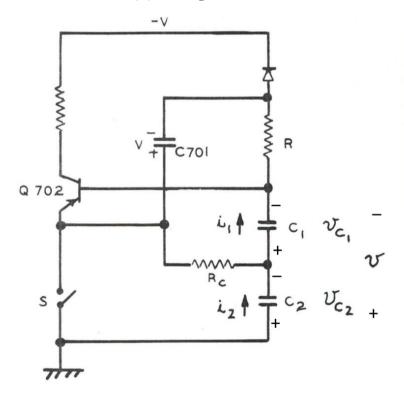

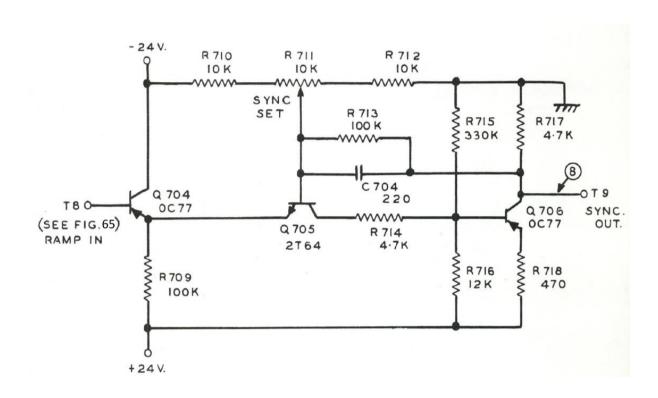

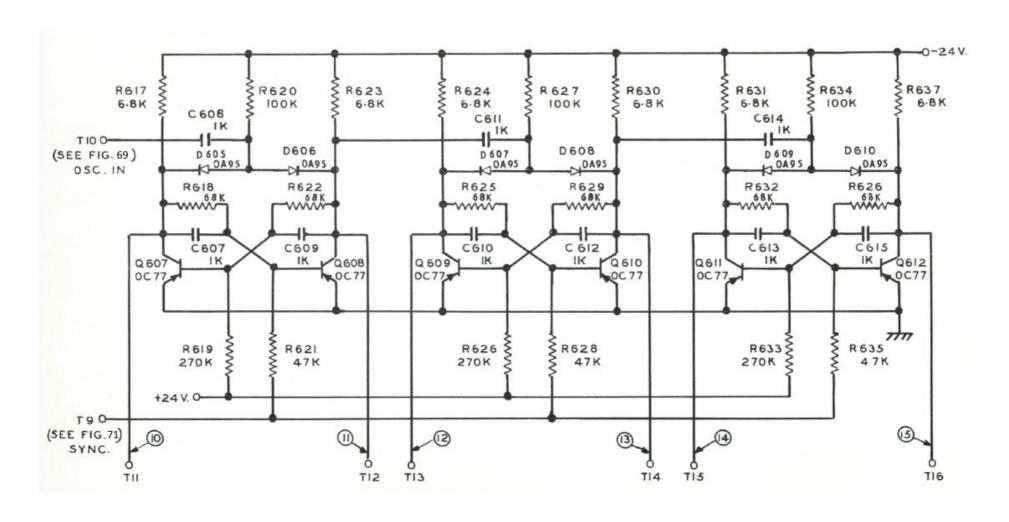

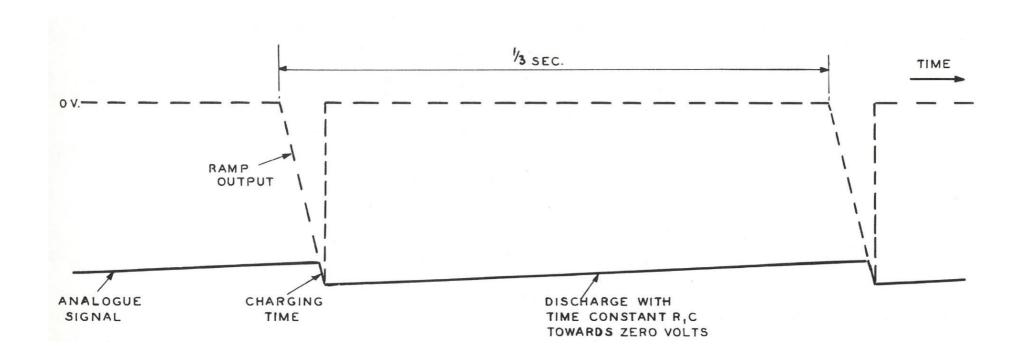

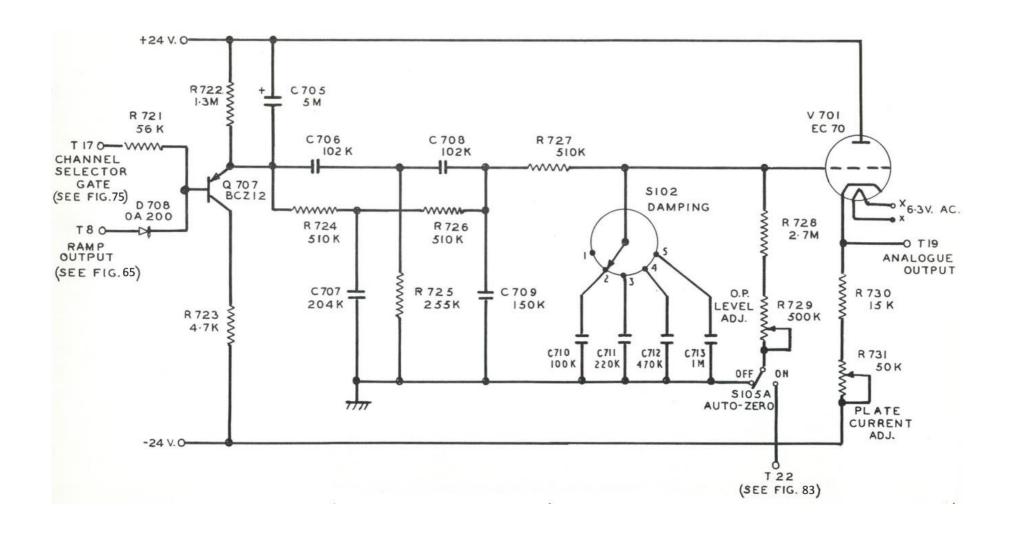

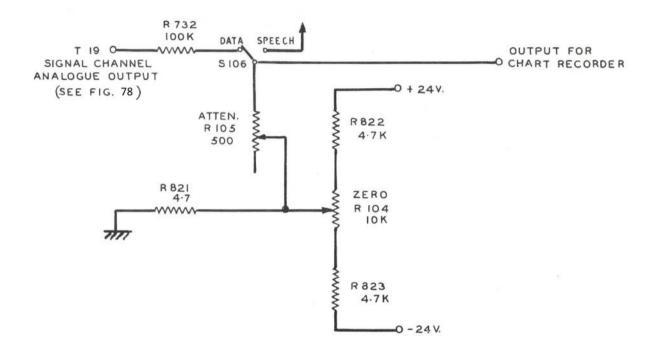

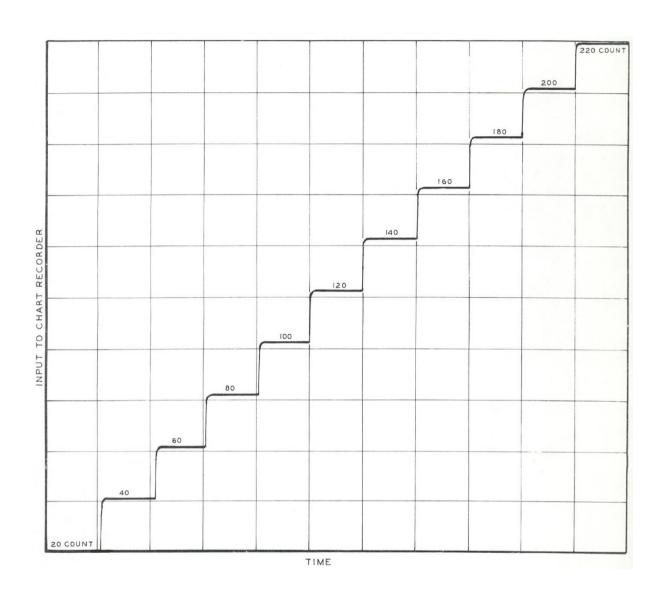

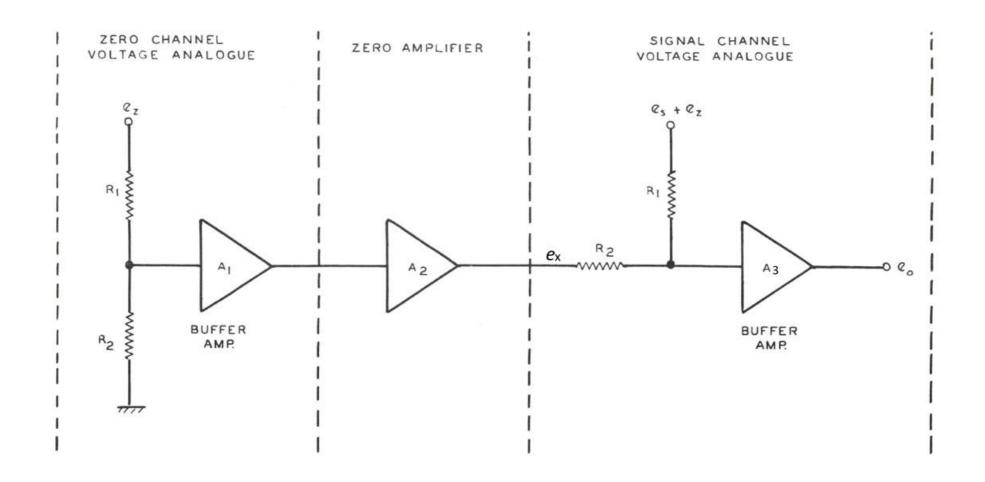

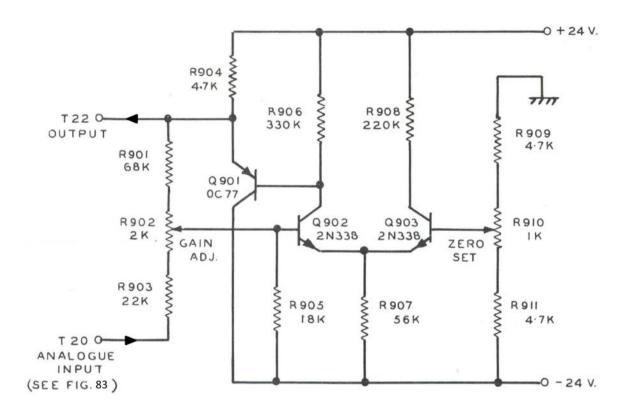

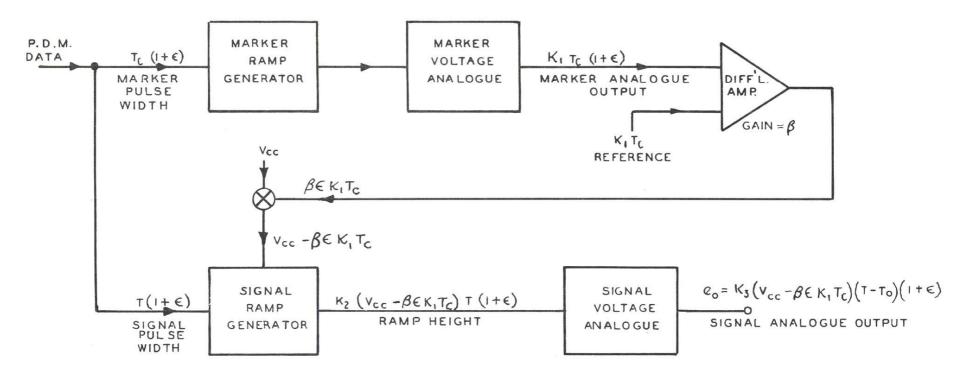

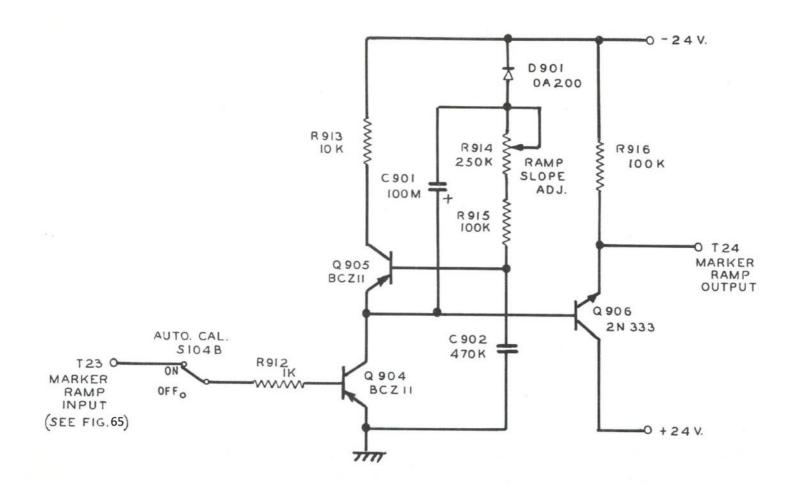

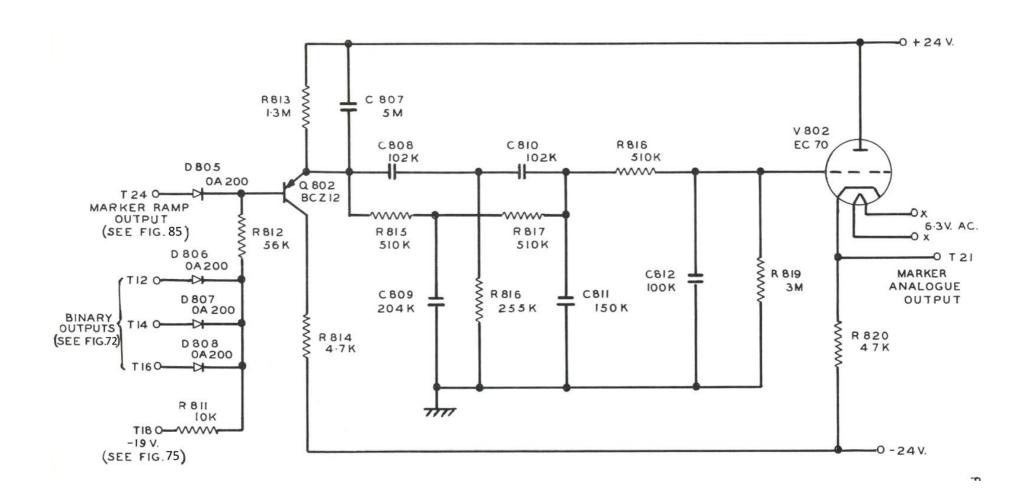

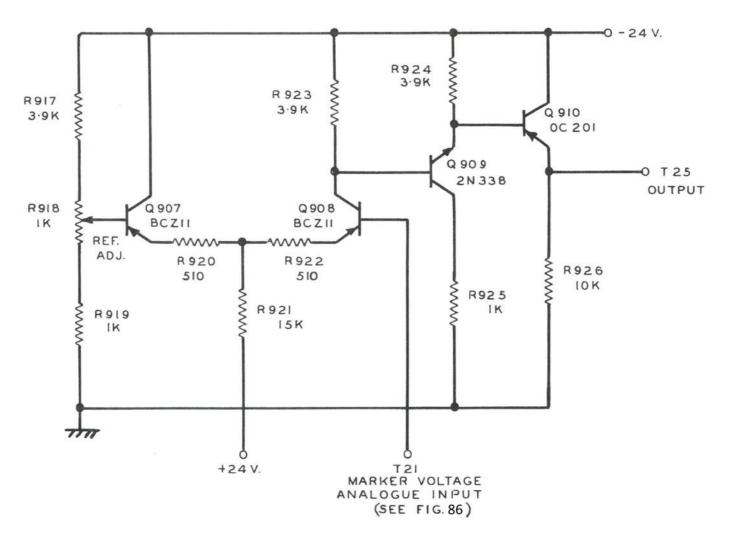

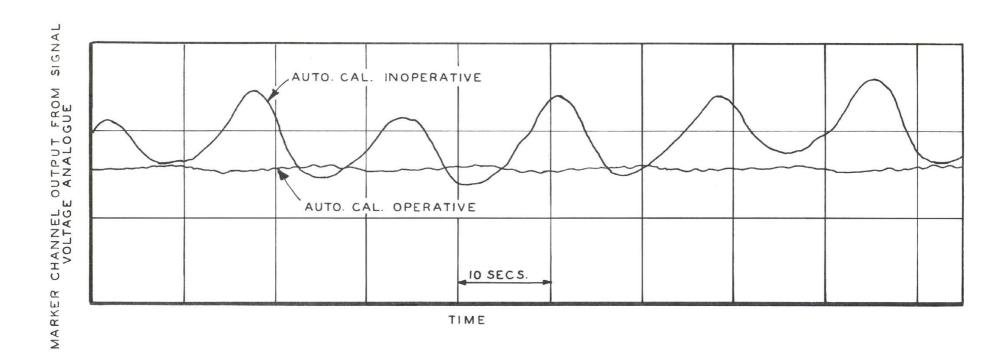

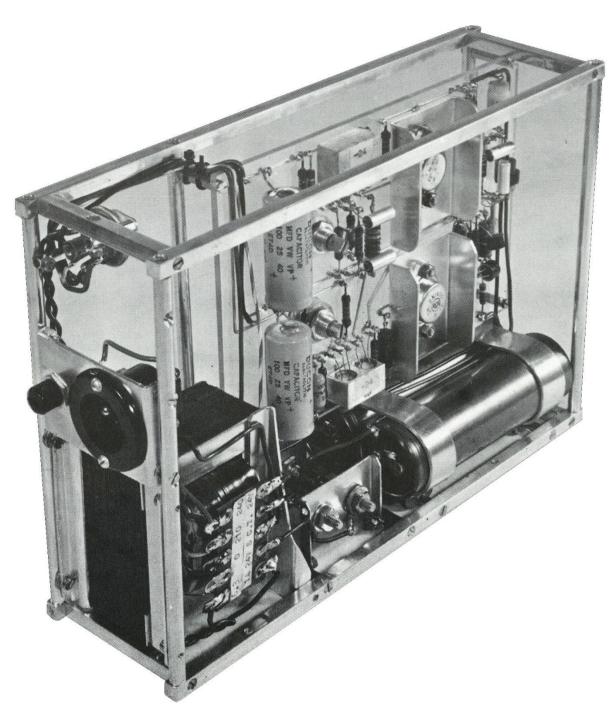

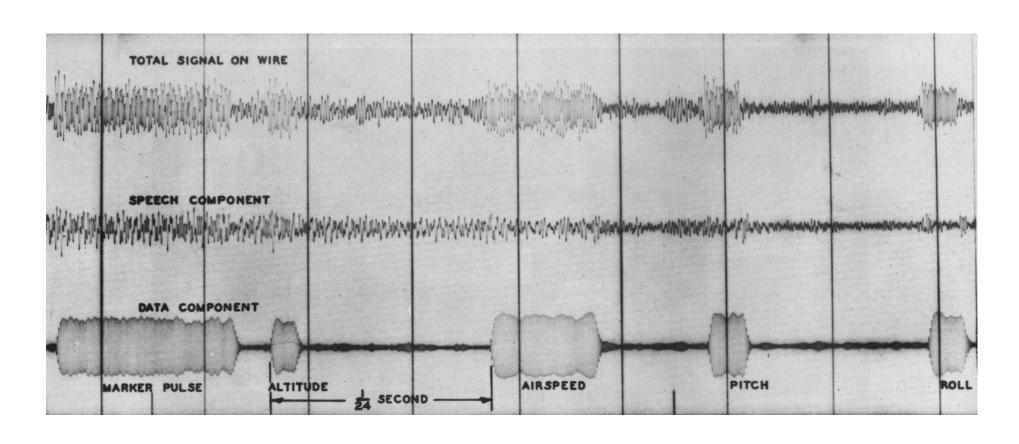

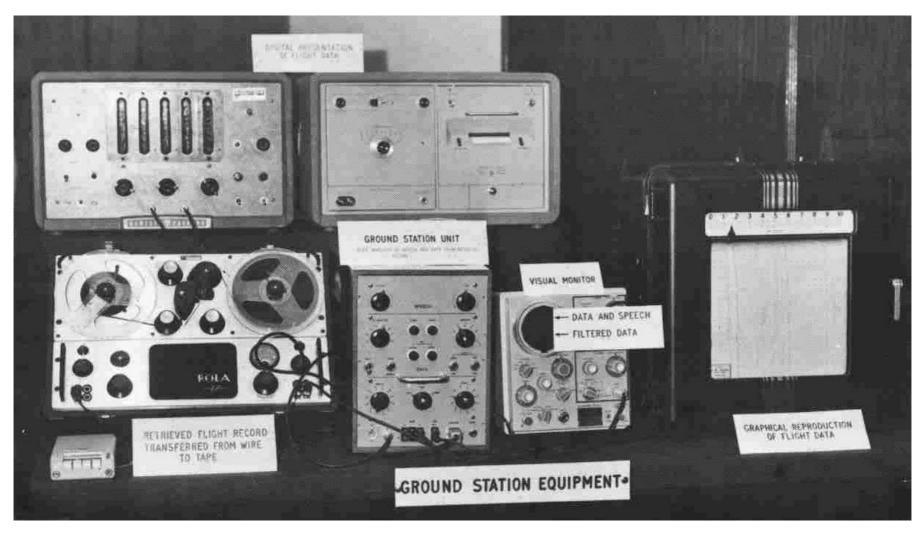

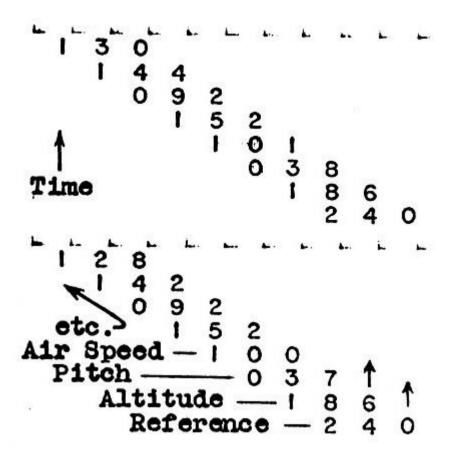

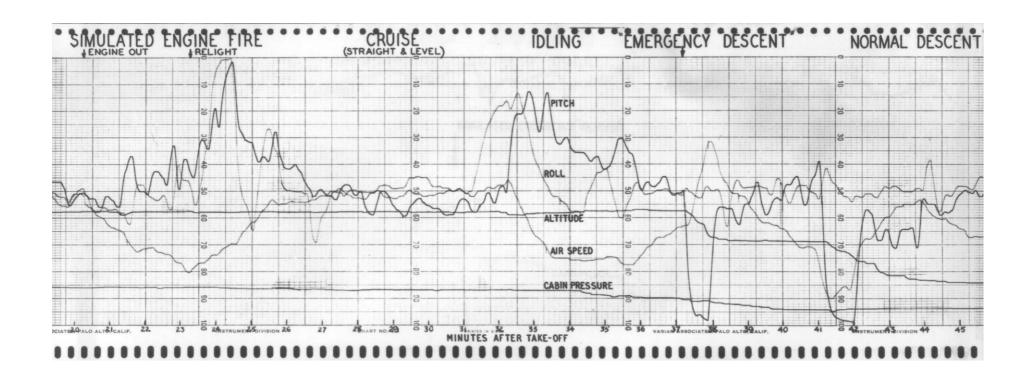

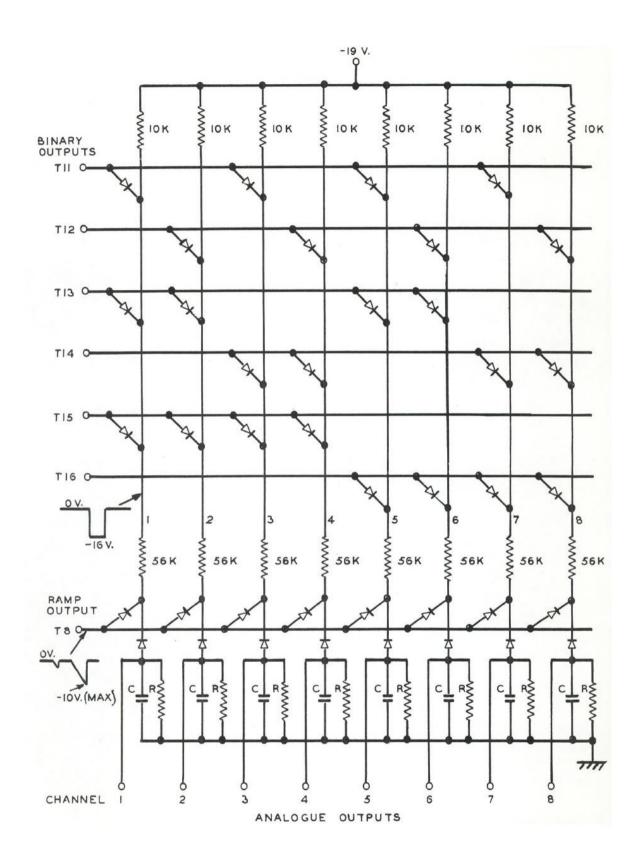

circuit of  $Q_4$  ensures that  $Q_4$  is "off" until the "on" pulse appears. If the supply voltage drops below  $\left(1 + \frac{R_1}{R_2}\right)V_Z$  the circuit switches back abruptly and the relay drops out.